LIBRARY OF THE UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

510.84 Il 6r no. 761 - 763 cop. 2

5/0,84 Tlby Tlby no. 761

AN ARRAY COMPUTER FOR THE CLASS OF PROBLEMS TYPIFIED BY THE GENERAL CIRCULATION MODEL OF THE ATMOSPHERE

D-1-

BY

Marvin L. Graham and D. L. Slotnick

December 1975

DEPARTMENT OF COMPUTER SCIENCE

UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN · URBANA, ILLINOIS

Report No. UIUCDCS-R-75-761

AN ARRAY COMPUTER FOR THE CLASS OF PROBLEMS TYPIFIED

BY THE GENERAL CIRCULATION MODEL OF THE ATMOSPHERE

by

Marvin L. Graham and D. L. Slotnick

December 1975

Department of Computer Science University of Illinois at Urbana-Champaign Urbana, Illinois 61801

<sup>\*</sup>This work was supported in part by NASA Goddard Space Flight Center under Grant No. US NASA NAS-5-23334 and was submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science, December 1975, for Marvin L. Graham.

510.x4 JC6r no 761-76=

## TABLE OF CONTENTS

|    |      |          |                                                     |    |   | Page |

|----|------|----------|-----------------------------------------------------|----|---|------|

| 1. | Intr | oduction | 1                                                   |    |   | 1    |

| 2. | The  | Problem  |                                                     |    | • | 3    |

|    | 2.1  | Genera   | l Circulation Models                                |    | • | 3    |

|    |      | 2.1.1    | Vertical Levels                                     | •  |   | 7    |

|    |      | 2.1.2    | Time                                                | •  |   | 7    |

|    |      | 2.1.3    | Horizontal Reoslution and Various                   |    |   |      |

|    |      |          | Differencing Schemes                                | •  |   | 9    |

|    | 2.2  | GISS M   | odifications to the Model                           | •  |   | 12   |

|    | 2.3  | The Ef   | fects of the Oceans on the Atmosphere               | •  |   | 13   |

|    | 2.4  | Input    | and Output Requirement of the Model                 | •  |   | 15   |

| 3. | The  | Array C  | omputer                                             |    |   | 18   |

| 4. | The  | System : | Design                                              |    |   | 23   |

|    | 4.1  | System   | Parameters                                          | •  |   | 23   |

|    |      | 4.1.1    | Word Size                                           | •  |   | 23   |

|    |      | 4.1.2    | Word Format                                         | •  |   | 24   |

|    |      | 4.1.3    | Memory Requirements                                 |    |   | 26   |

|    |      | 4.1.4    | Measurements of the GISS Model                      | •  |   | 27   |

|    |      | 4.1.5    | Processor Speed Requirements                        | •  |   | 29   |

|    |      | 4.1.6    | The Choice of TTL Technology for the Processor      | •  |   | 30   |

|    | 4.2  | The Pr   | ocessor Design                                      | •  |   | 34   |

|    |      | 4.2.1    | Convention Used in the Figures Which Describe Logic |    |   | 36   |

|    |      | 4.2.2    | Signal Name Notation Used in the Design Description | ١. | • | 38   |

|    |      | 4.2.3    | Inversion in the Logic Figures                      | •  |   | 39   |

|    |      |         |                                                         | Pa | age |

|----|------|---------|---------------------------------------------------------|----|-----|

|    |      | 4.2.4   | Detailed Description of Two Packages                    | •  | 39  |

|    |      | 4.2.5   | The Processor Design                                    | •  | 42  |

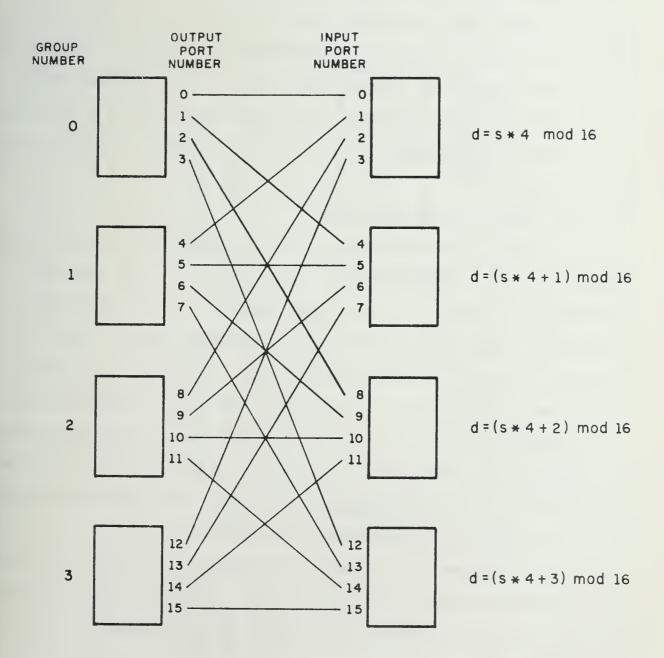

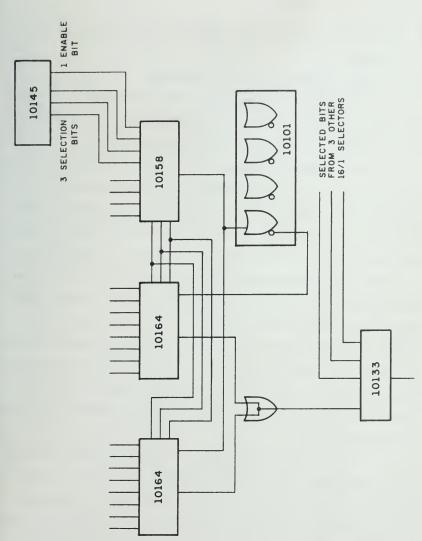

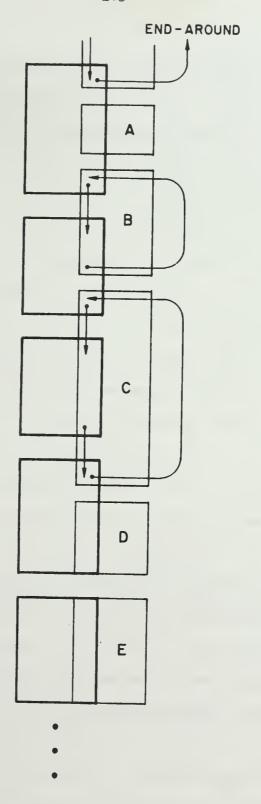

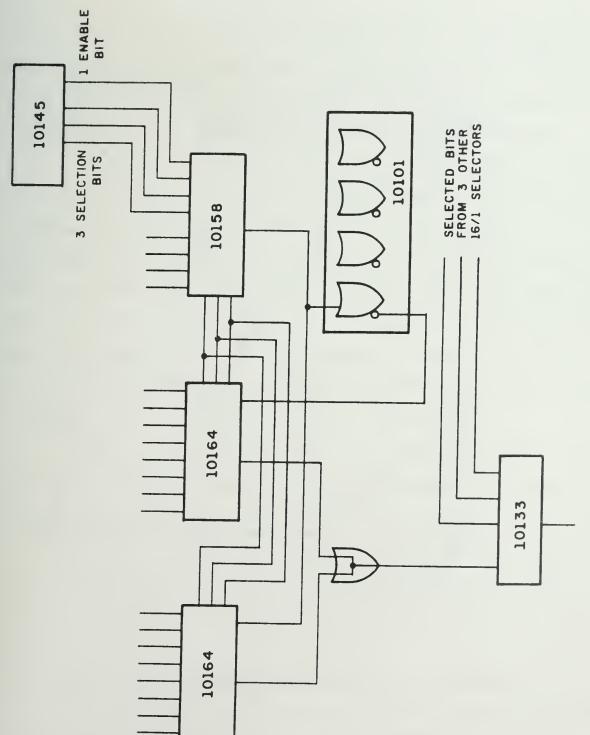

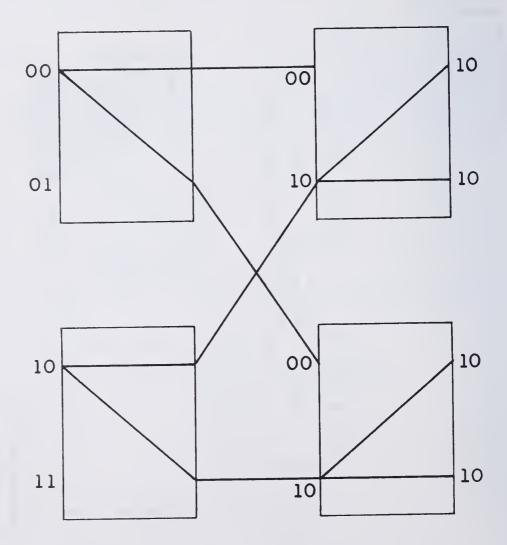

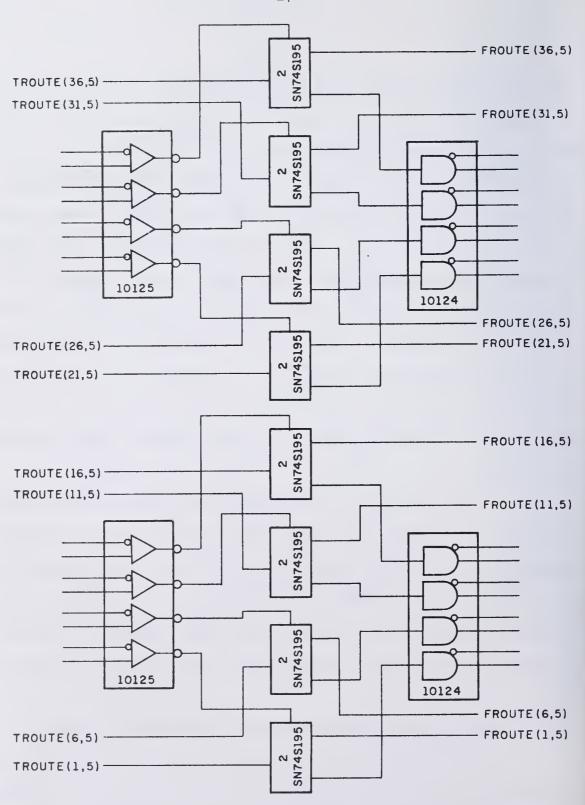

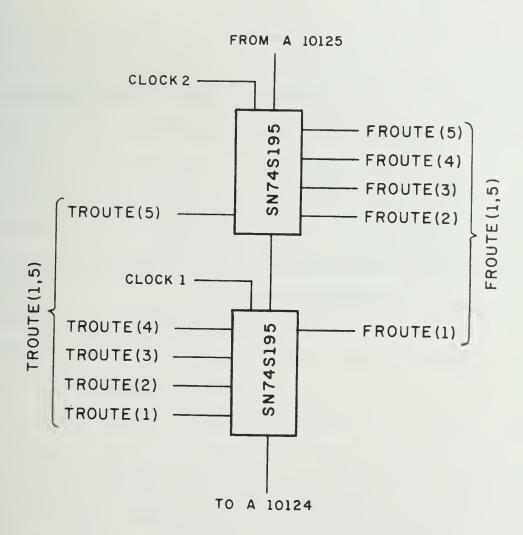

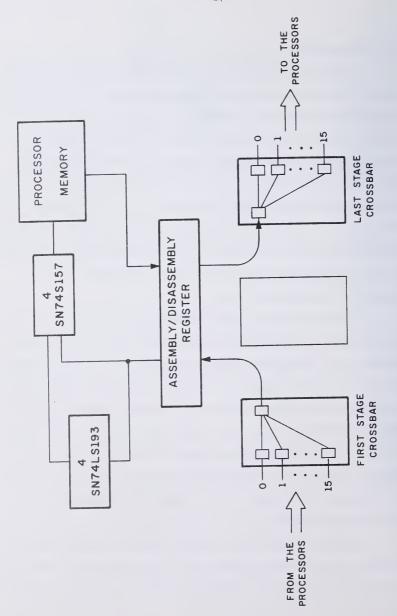

|    | 4.3  | Proces  | sor Intercommunication - The Routing Network            | •  | 155 |

|    |      | 4.3.1   | Routing Network Control                                 |    | 158 |

|    |      | 4.3.2   | ECL Logic                                               | •  | 162 |

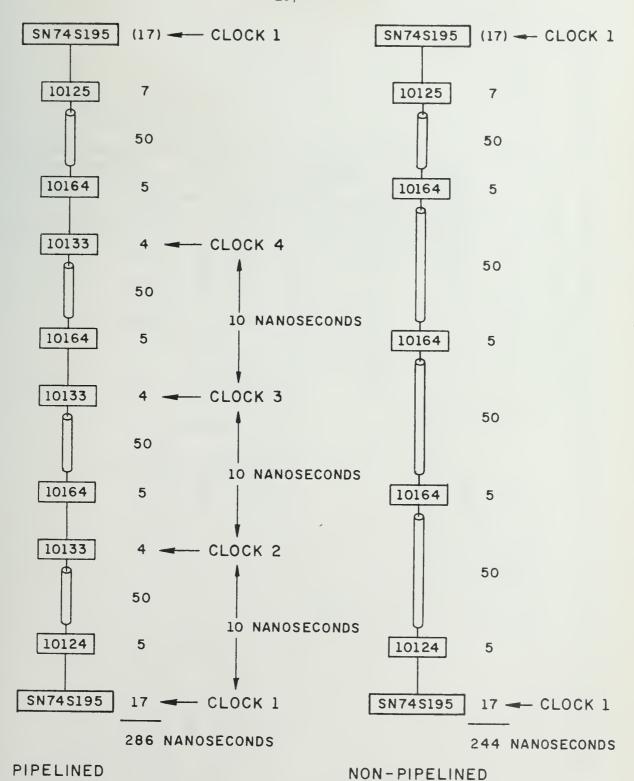

|    |      | 4.3.3   | Routing Network Time and Component Count Estimates      | •  | 164 |

|    |      | 4.3.4   | Table Look Up                                           | •  | 177 |

|    |      | 4.3.5   | Communication with the Control Unit and the             |    |     |

|    |      |         | Input-Output Channel                                    |    | 179 |

|    | 4.4  | The Co  | ontrol Unit                                             |    | 181 |

|    |      | 4.4.1   | Control of the Processor Array                          | •  | 181 |

|    |      | 4.4.2   | Control of the Routing Network                          | •  | 183 |

| ·  | Desi | gn Test | ting                                                    |    | 185 |

|    | 5.1  | The Lo  | ogic Simulation System                                  |    | 185 |

|    |      | 5.1.1   | The Logic Simulator Language and the Preprocessor       |    | 188 |

|    |      | 5.1.2   | Timing by the Simulator                                 | •  | 191 |

|    |      | 5.1.3   | Debugging Aides in the Simulation System                |    | 193 |

|    |      | 5.1.4   | Simulated Packages with No Exact Hardware Analog        |    | 195 |

|    |      | 5.1.5   | Loops                                                   |    | 196 |

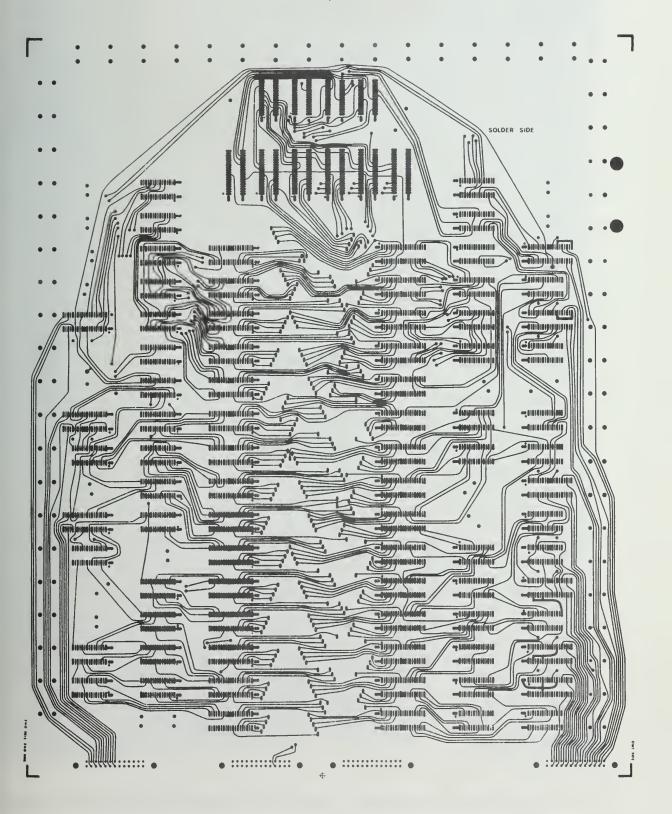

|    |      | 5.1.6   | Wiring Lists                                            |    | 209 |

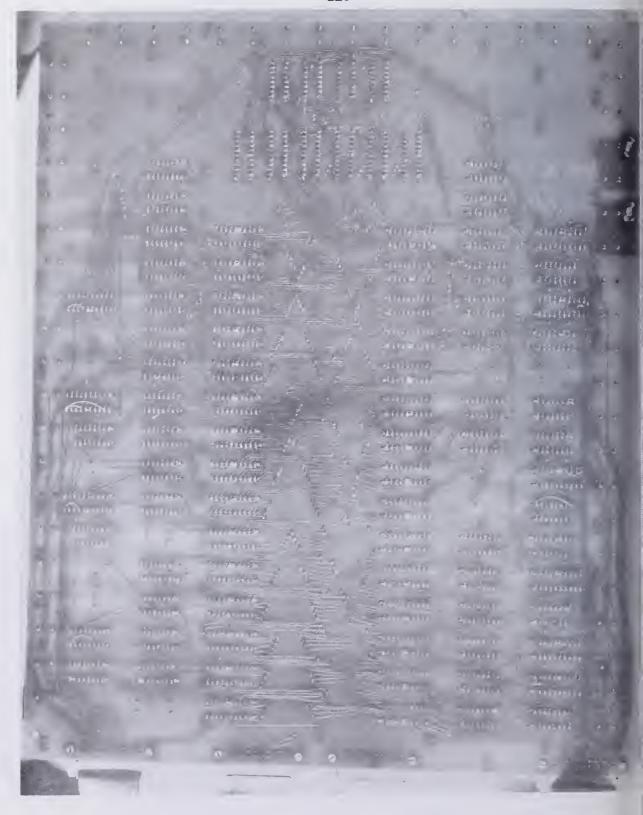

|    | 5.2  | The M   | ultiplier Prototype                                     | •  | 210 |

| 6. | Sys  | tem Per | formance                                                | •  | 219 |

|    | 6.1  | Proce   | ssor and Routing Unit Cycle Times                       | •  | 219 |

|    | 6.2  | Perfo   | rmance of the System on the General Circulation Model . |    | 221 |

|      |       |         |                                            |      |      |    |    | ] | Page |

|------|-------|---------|--------------------------------------------|------|------|----|----|---|------|

|      |       | 6.2.1   | The Rectangular Model                      |      |      |    | •  | • | 227  |

|      |       | 6.2.2   | The Split Grid Model                       | • •  |      |    | •  |   | 228  |

|      |       | 6.2.3   | The Polar Circle Sum                       |      |      | •  | •  |   | 231  |

|      |       | 6.2.4   | A Hardware and Time Comparison of the Clos | , On | nega | ar | ıd |   |      |

|      |       |         | Nearest Neighbor Routing Schemes           |      |      | ٠  | •  | • | 231  |

|      | 6.3   | Image : | Data Processing                            |      |      |    | •  | • | 234  |

|      |       | 6.3.1   | Image Data Clustering                      |      |      |    | •  | • | 235  |

|      |       | 6.3.2   | Image Data Classification                  |      |      |    | •  |   | 237  |

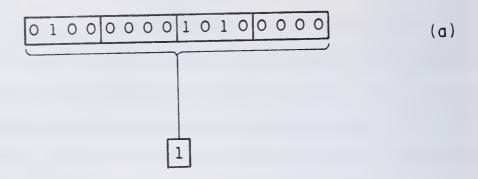

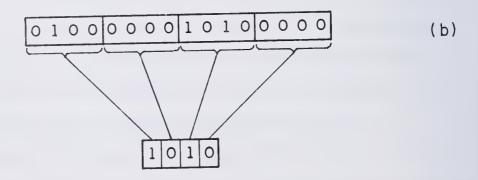

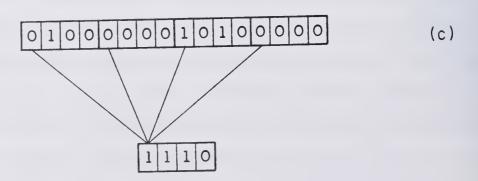

|      |       | 6.3.3   | Byte Packing and Unpacking                 |      |      | •  | •  |   | 239  |

|      | 6.4   | File P  | cocessing and Information Retrieval        |      |      | •  |    |   | 243  |

|      |       | 6.4.1   | File Statistics                            | • •  |      | •  | •  |   | 243  |

|      |       | 6.4.2   | Information Retrieval                      |      |      |    | •  |   | 244  |

|      | 6.5   | Matrix  | Inversion by Gaussian Elimination          |      |      | •  | •  | • | 245  |

|      |       | 6.5.1   | Solution of Inhomogeneous Systems          |      |      |    | •  |   | 245  |

|      |       | 6.5.2   | Inversion of a Matrix                      |      |      |    | •  |   | 253  |

| 7.   | Oper  | ating P | arameters of the System                    |      |      |    | ٠  |   | 254  |

| 8.   | Conc  | lusion. |                                            |      | • •  |    | •  | • | 263  |

| Refe | erenc | es      |                                            |      | •    |    | •  |   | 264  |

| Appe | endix |         |                                            |      | •    |    |    | • | 269  |

| VITA | Α     |         |                                            |      |      |    |    |   | 293  |

## 1. Introduction

a computer suited to the class of problems typified by the general circulation model of the atmosphere. The research was supported in large part by the Goddard Institute for Space Studies (GISS) of the National Aeronautics and Space Administration (NASA). The needs that prompted GISS to support the research imposed several practical constraints on the design which was sought. A fundamental goal was that the machine which resulted from the design was to have roughly 100 times the computing capability of the GISS IBM 360/95 which is now used for research with a general circulation model. Their desire to increase the spatial resolution of that model by refining the grid implied the need for a 100 fold increase in computing capability to stay even in terms of the real time.

A second requirement was that the resulting machine be programmable in a higher level language similar to FORTRAN. The current model is written almost entirely in FORTRAN, and the GISS staff planned to modify an existing compiler for CFD - a FORTRAN-like language - for ILLIAC IV for use with their new machine. Moreover, the new machine was to cooperate in the general circulation experiments on the expanded models with the IBM 360/95; the IBM machine would continue to be used for the pre-processing and post-processing of model data which it now performs for the smaller model which it also now executes. The implication of the FORTRAN and IBM machine constraints is that the machine possess floating point arithmetic capability, and that the floating point format of the machine be close to that of the IBM 360 series.

A third constraint on the design was that the cost of the machine resulting from the design effort was to be significantly less than that of

other extant machines of similar computing capability. Among these are the ILLIAC IV, the Texas Instruments Corporation Advanced Scientific Computer, and the Control Data Corporation STAR.

A final constraint on the design was that it be feasible to fabricate a complete system and put it in operation by early 1978. A clear implication of this and the preceding constraint is that there is neither time nor money for the development of new hardware families, let alone new chips. The design will have to be made in terms of an existing hardware family with components readily available off-the-shelf.

### 2. The Problem

Several groups in the United States are working on global general circulation models. The three largest efforts are those of Mintz and Arakawa at UCLA (Arakawa, 1972; Mintz, 1974), Smagorinsky and Manabe at the Geophysical Fluid Dynamics Laboratory (GFDL) (Smagorinsky, 1963) and Kasahara and Washington at the National Center for Atmospheric Research (Kasahara, 1967). The UCLA model is of primary interest to this research because the model run by GISS (Tsang, 1973) is a modified form of that model.

#### 2.1 General Circulation Models

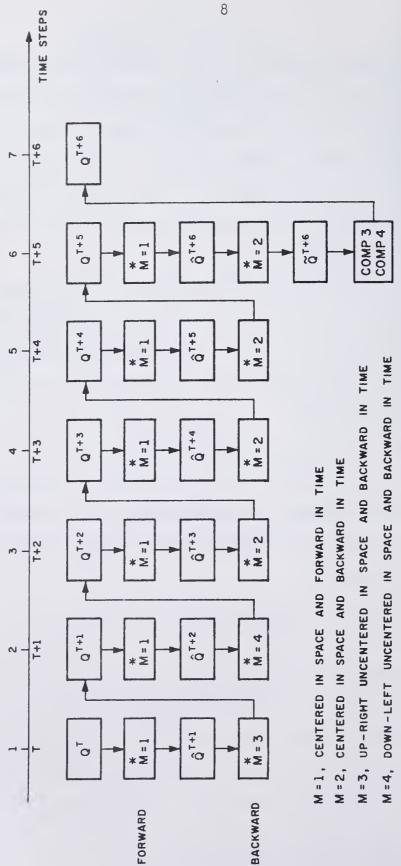

A general circulation model simulates the behavior of a three dimensional spherical atmosphere on a digital computer. The bulk of the computing load necessary in the simulation is the time integration of the equations of fluid dynamics of the atmosphere. In the UCLA model, subroutines called COMP1 and COMP2 perform this time integration of the equations of motion. Every six cycles through COMP1-COMP2, the effects of solar radiation in heating the atmosphere and the effects of evaporation, condensation and precipitation are introduced through the execution of the COMP3 and COMP4 subroutines. The process is shown in Figure 2.1.2-1. Every four cycles through the process illustrated by Figure 2.1.2-1, a table lookup process is used to introduce the effects of long-wave infra-red energy absorbtion in the GISS model.

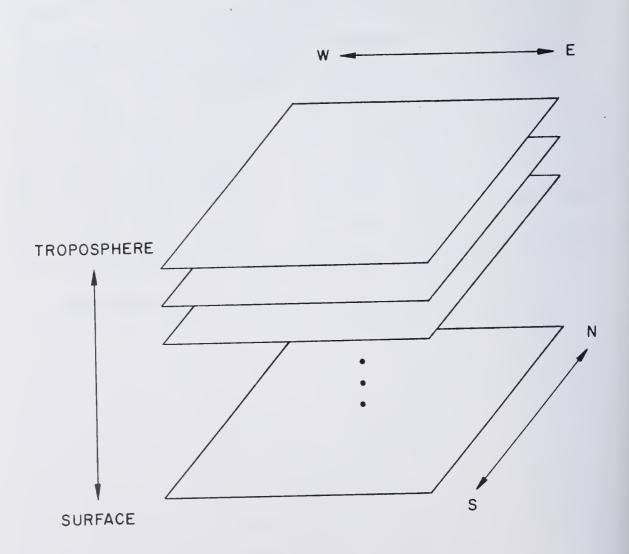

Table 2.1-1 lists the parameters which define the conditions under which the model operates. Table 2.1-2 lists the variables of the model and gives their spatial dimensions. Figure 2.1-1, which is taken from a GISS

#### Prescribed parameters.

To use the atmospheric general circulation model, for this or any other planet, the following parameters must be prescribed:

Radius, surface gravity and rotation speed of the planet.

Solar constant, and orbital parameters of the plant.

Total atmospheric mass.

Thermodynamical and radiation constants.

Geographical distributions of open ocean, ice covered ocean,

bare land and land covered by glacial ice.

Elevation of the bare land and glacial ice.

Surface roughness.

Thickness of the sea ice.

Ocean surface temperature.

Table 2.1-1. The Parameters of the General Circulation Model

## Variables of the Atmospheric Model

| Horizontal Velocity                              |                      |

|--------------------------------------------------|----------------------|

| West to East component                           | U(X,Y,Z)             |

| South to North component                         | V(X,Y,Z)             |

| Temperature                                      | T(X,Y,Z)             |

| Water Vapor (specific humidity)                  | q(X,Y,Z)             |

| Surface Atmospheric Pressure                     | p <sub>0</sub> (X,Y) |

| Parameters of the Planetary Boundary Layer (PBL) |                      |

| Boundary Layer Depth                             | (Y, X)               |

| Temperature Discontinuity at the PBL             | (Y,Y)                |

| Moisture Discontinuity at the PBL                | (Y, X)               |

| Parameters of the Earth's Surface                |                      |

| Ground Temperature                               | (Y,Y)                |

| Ground Water Storage                             | (Y,Y)                |

| Mass of Snow on the Ground                       | (Y,Y)                |

| A Future Variable of the Atmospheric Model       |                      |

| Ozone Concentration                              | (X,Y,Z)              |

Table 2.1-2 The Variables of the General Circulation Model and their Dimensionalities

$$\frac{dV}{dt} + f\mathbf{k} \times \mathbf{V} + \nabla_{\sigma} \Phi + \sigma \alpha \nabla \pi = \mathbf{F}$$

$$\frac{\partial \pi}{\partial t} + \nabla_{\sigma} \cdot (\pi \mathbf{V}) + \frac{\partial}{\partial \sigma} (\pi \dot{\sigma}) = 0$$

$$p\alpha = RT$$

$$\frac{d\theta}{dt} = \frac{1}{c_p} \frac{\theta}{T}Q$$

$$\frac{1}{\pi} \frac{\partial \Phi}{\partial \sigma} = -\alpha$$

$$\frac{dq}{dt} = -C + E$$

#### Here the notation is

- V horizontal velocity

- t time

- f Coriolis parameter

- k vertical unit vector

- $\nabla_{\sigma}$  two-dimensional gradient operator

- σ the vertical coordinate [ =  $(p-p_t)/(p_s-p_t)$ ]

- p pressure

- p, pressure at top of model atmosphere, constant

- p pressure at bottom of model atmosphere

- α specific volume

- $\pi$   $p_s p_t$

- F horizontal frictional force

- R gas constant

- T temperature

- θ potential temperature

- $c_n$  specific heat at constant pressure

- Q heating rate per unit mass

- Φ geopotential

- q water vapor mixing ratio

- C rate of condensation

- E rate of evaporation.

Figure 2.1-1 The Primitive Equations and the Variables of the GISS General Circulation Model.

report on the model (Somerville, 1974), shows the basic equations of the model. The remainder of this section will describe the UCLA and GISS models. The emphasis will be on describing the differences between the first UCLA model (Arakawa, 1972), the GISS model which evolved from it (Somerville, 1974; Tsang, 1973) and the second UCLA model (Mintz, 1974) to illustrate the range over which variations of the current GISS model may run in future models.

#### 2.1.1 Vertical Levels

The first UCLA model had only three vertical levels. The current GISS model has nine, and the second UCLA model has twelve. GISS hopes to expand to a fifteen level model. The new UCLA model incorporates a special "sponge layer" as its highest level to damp out spurious numerical wave reflections (Mintz, 1974).

## 2.1.2 <u>Time</u>

The first UCLA model and the GISS models use the explicit matsuno predictor-corrector method for advancing time. For a variable Q, the scheme uses a forward and a backward step to advance time by one interval in the following way:

Forward

$$\frac{\hat{Q}(t_{n+1}) - Q(t_n)}{t_{n+1} - t_n} = f'(Q(t_n))$$

Backward

$$\frac{Q(t_{n+1}) - Q(t_n)}{t_{n+1} - t_n} = f'(Q(t_{n+1})*)$$

The forward step uses the current values of the variable and the function f', which approximates the derivative, to produce an estimate,  $\hat{Q}(t_{n+1})$ , for the value of the variable at the next time. The backward step uses the estimated value to compute  $Q(t_{n+1})$ , the value of the variable at the next time. The process is illustrated by Figure 2.1.2-1.

\* = COMP1 - COMP2

Figure 2.1.2-1

Differencing in the Time Integration Procedure

The Sequence of Time Steps and Spatial

The GISS version of the model for the IBM 370/165 takes advantage of the fact that only one complete copy of the variables is needed for this method to reduce the storage requirements of the model by roughly half.

The new UCLA model uses the leapfrog scheme to advance time. This scheme computes a value for the variable A at time  $t_{n+1}$  as follows:

$$\frac{A(t_{n+1}) - A(t_{n-1})}{2(t_{n+1}) - t_n} = f'(A(t_n)).$$

This scheme takes half the computer time, but requires twice the space of the Matsuno scheme, since two complete sets of the variables are required to compute a new value. The leapfrog scheme is numerically superior to the Matsuno scheme in that it does not amplify or damp the solution, but it is inferior in that it tends to produce two separate and divergent solutions. The new UCLA model will couple these two solutions by introducing one Matsuno step for every six leapfrog steps.

Figure 2.1.2-1, taken from Tsang (1973), shows the sequence of computation in the current UCLA and GISS models. Each normal time step conisists of a COMP1-COMP2 call for a forward (estimator) time step and another COMP1-COMP2 call for a backward (corrector) step. Every six normal steps, the effects of solar radiation and evaporation are computed by a call on COMP3 and COMP4. The value of the variable M determines which form of the difference algorithm will be used in the COMP1-COMP2 routines. The following section discusses the need for the spatial difference variations.

# 2.1.3 Horizontal Resolution and Various Differencing Schemes

Both UCLA models and the most frequently used version of the GISS model have 72 points around circles of latitude, and 46 circles of latitude

from pole to pole (including the poles). For the next decade GISS is interested in models of two different sizes for the proposed computer (Halem, 1974) Both models will have 15 vertical levels (i.e., 15 spherical shells) and differ only in the number of points around the equator of the model. The two sizes of interest are:

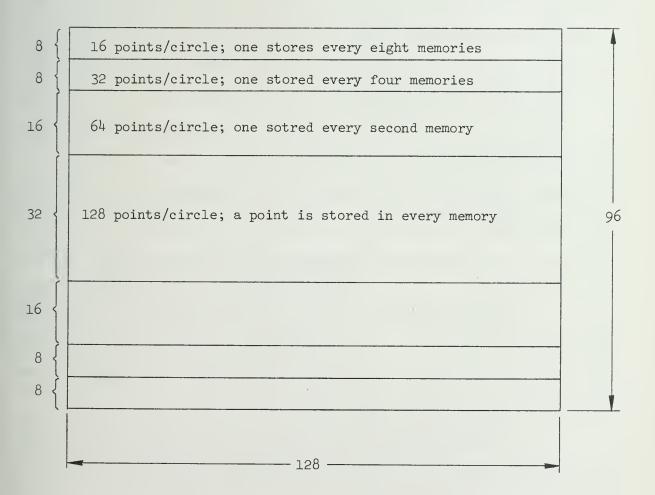

- 1. A model with 128 points around the equator and with 96 circles of latitude. We will call this the 96 x 128 grid.

- 2. A model with 256 points around the equator and with 192 circles of latitude. We will call this 192 x 256 grid.

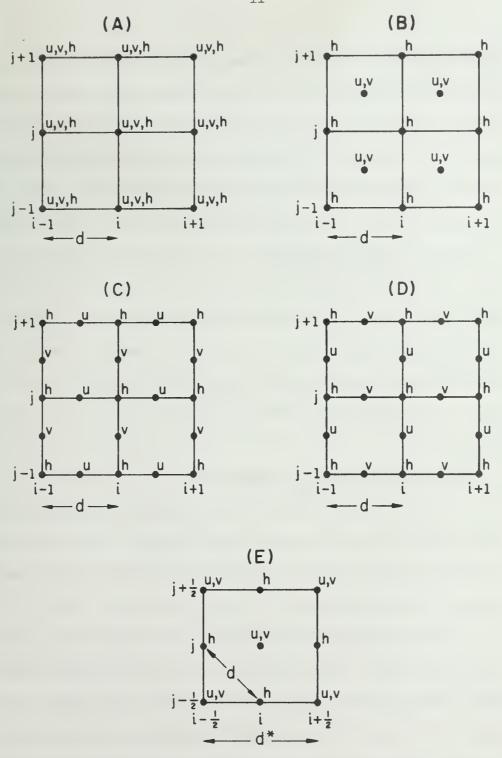

values of the primary meteorological variables at different points in space. Figure 2.1.3-1, which is taken from (Mintz, 1974), shows five grid schemes which have been considered. The first UCLA model and the current GISS model use scheme B. Arakawa has decided to use scheme C in the new UCLA model. The basis for this decision, which follows in the next paragraph, illustrates the intricacy of the model.

Convection of moisture from the earth's surface to high altitudes, called cumulus convection, is an important atmospheric phenomenon, especially in the tropics. The scale of this motion is tens of kilometers; the distance between grid points at the equator is 156 kilometers even for the 256 point model. Arakawa found a means to parameterize cumulus cloud convection so that its effects could be felt by the model in spite of the fact that direct simulation — as the model does for winds, temperature and specific humidity — is not possible. The parameterized cumulus convection produces rising and subsiding air motion which frequently occurs in a

- u: the west to east component of the horizontal flow

- v: the south to north component of the horizontal flow

- h: the distance from the surface to the top of the atmosphere in the model

Figure 2.1.3-1 Staggered Grid Schemes

checkerboard pattern. To use scheme B for the grid layout, one must average the values of pressure at the corners of each grid square to compute the effect of pressure on the flow fields. Rising motion at one corner is cancelled by subsidence at another, and the net effect is that the cumulus convection goes unnoticed by the model. Arakawa devised the intricate time and space difference scheme shown in Figure 2.1.2-1 (taken from Tsang, 1973) to counteract this insensitivity. The differencing scheme uses a cycle of space centered and uncentered differences to permit the checkerboard pattern produced by cumulus convection to influence the model. When grid scheme C is used, these elaborate gyrations are unnecessary. Primarily for this reason, Arakawa has decided that scheme C will be used in the next UCLA model. The current model, which is the basis for the GISS work, uses scheme B.

## 2.2 GISS Modifications to the Model

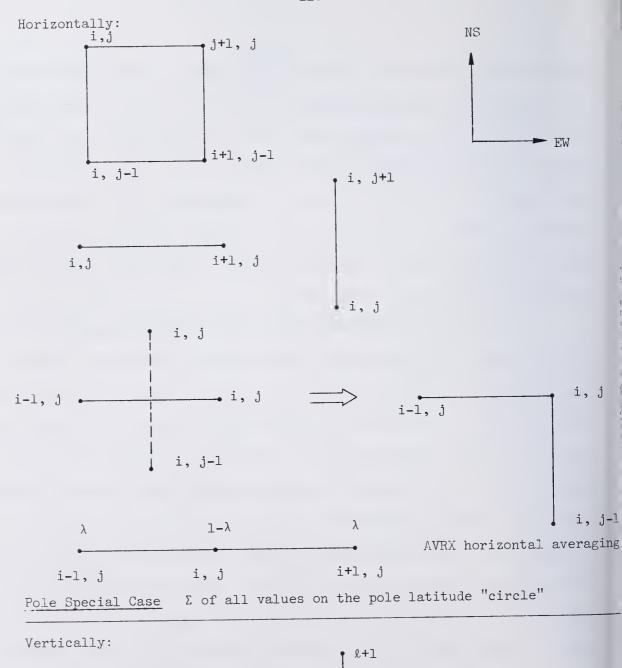

Several modifications of the UCLA model were made by GISS. Only one of these has a major impact on this research. This is the distinctly different approach to the treatment of high latitude regions which GISS has adopted, and which they call the split grid model.

The meridian lines on a sphere get progressively closer as they approach the poles. The Courant stability criterion (Fox, 1961), c  $\Delta t < \Delta x$ , where c is the highest velocity in the model, requires that a very small time step be used to avoid numerical instability in these regions. The UCLA approach to this problem is to smooth across progressively wider bands of meridional lines as the meridians get closer together. The GISS approach is to progressively reduce the number of meridians by a factor of two as one moves from the equator to the poles. This divides the sphere into several

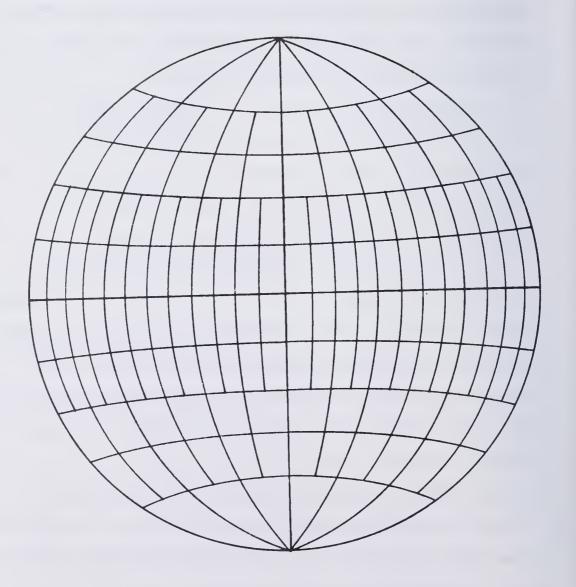

regions as illustrated in Figure 2.2-1. Within each region, the number of meridians is constant. The region boundaries are chosen to keep the intermeridian distance roughly constant for all regions. In the split grid model, the need for zonal smoothing is much reduced but not completely eliminated. Table 2.2-1 shows the number of split grid regions for grids with different numbers of points on the equator.

| Meridians at the equator | Number of split grid regions |

|--------------------------|------------------------------|

| 72                       | 5                            |

| 128                      | 7                            |

| 256                      | 11                           |

| 512                      | 15                           |

Table 2.2-1. The Number of Split Grid Regions for Various Model Sizes

The split grid model offers two advantages over the UCLA smoothing approach. The first is that a larger time step can be used throughout the model, since the smallest increment in the "x" direction is larger in a split grid model. Also, there is a potential storage saving for the split grid model. The split grid scheme does have the liability that it is more difficult to program.

Whether a rectangular UCLA-style model or a GISS split grid model is used, some averaging of polar values must be done. Thus, there is a clear inherent parallelism in the processing which strongly suggests parallel computation on circles of constant latitude.

# 2.3 The Effects of the Oceans on the Atmosphere

Until recently, meteorologists have assumed that the effects of the oceans on heat transfer from the equator to the high latitude regions was negligible. Lately, however, this view has changed, as evidenced by the

Figure 2.2-1 The GISS Split Grid Model

relatively large emphasis on ocean modelling at the UCLA workshop (Mintz, 1974), and by the decision of the UCLA group to couple an ocean model and an atmospheric model in a future model. Whereas the atmospheric equations are integrated in time by explicit numerical methods, Semptner of the UCLA staff indicated that all known ocean models advance time by successive over-relaxation - an implicit method (Semptner, 1974). He also feels that IBM 360 single precision arithmetic is sufficient for solving the system of equations for a 46 x 72 grid.

Sempther also cited work at GFDL (Manabe, 1969) which indicates that integration of the atmospheric equations consumes 40 times the amount of computer time as does integration of the ocean equations for the same simulated time. This dramatic difference results from the differences in the two fluids, and the fact that the implicit solution scheme permits the use of significantly larger time step than an explicit scheme would.

While it is clear that an ocean model will be required to improve current results, it is not clear what the details of the ocean model must be. Recent observations and numerical work (Mintz, 1974) have shown the existence of small scale (40-50 kilometer) ocean phenomena. Whether these are important, and if so, whether their effects can be parameterized (as was cumulus convection in the atmospheric model) is yet to be shown. The potential need for an ocean model coupled to the atmospheric model will be most explicitly reflected in the size of memory that we recommend.

# 2.4 Input and Output Requirement of the Model

The proposed mode of operation for the new machine is that it receive its program and initial data from the GISS IBM 360/95 by using an IBM channel with a data handling capacity of  $6(10)^6$  bits per second.

A problem thus received would be run in stand-alone fashion by the machine with periodic dumps of model status. The current GISS model writes an output record every two hours of simulated model time for a  $46 \times 72 \times 9$  grid. Table 2.4-1 shows the variables which constitute these records, the sizes of the records for a  $46 \times 72 \times 9$ ,  $96 \times 128 \times 15$ , and a  $192 \times 25 \times 15$  grid, the lower bound on the elapsed time to write the record using the channel at its maximum rate, and an estimate of the computing time required for the new machine to compute two hours of model simulation.

|                                                       |             | BYTES         |                |

|-------------------------------------------------------|-------------|---------------|----------------|

| DATA                                                  | 46 x 72 x 9 | 96 x 128 x 15 | 192 x 256 x 15 |

| TAU                                                   | 14          | 14            | 14             |

| c(300)                                                | 1,200       | 1,200         | 1,200          |

| Q(NS,EW,V,4)                                          | 476,928     | 2,949,120     | 11,796,480     |

| P (NS,EW) TS (NS,EW) SHS(NS,EW) GT (NS,EW) CW (NS,EW) | 13,248      | 49,152        | 196,608 each   |

| Total                                                 | 544,372     | 3,196,084     | 12,780,724     |

| Transmission<br>Time                                  | 0.726       | 4.26          | 17.04 Seconds  |

| Estimated<br>Computation<br>Time                      | 0.031       | 0.39          | 3.15 Seconds   |

Table 2.4-1 Record Sizes and Transmission times for Various Grid Sizes

As Table 2.4-1 makes clear, data output from the model will have to come at less than two hour simulated time intervals if the machine is not to become heavily output bound. It is doubtful that channel transmission capacity can be increased nearly enough to reduce to output time significantly with respect to the computation time.

## 3. The Array Computer

A computing capability improvement by a factor of 100 over the capability of the 360/95 is a big order. In the time span specified for the development of this design, there is no hope of achieving this improvement purely by increased raw hardware speed. Indeed, physical realities such as the bound imposed by the speed of propagation of electromagnetic waves may make this path forever impossible. Clearly, if the capability increase can be achieved, it must be achieved by using a machine organization different from that of the 360/95.

The approach we shall take is to organize the machine as an array processor. Applications research (Carroll, 1967) for an early array processor, the SOLOMON (Slotnick, 1962), has shown that the array processor organization is ideally suited to the class of problems that the general circulation model typifies: solution of partial differential equations on a large grid. Indeed, the GISS general circulation model has been successfully converted for execution on the ILLIAC IV (Slotnick, 1968), the only operational large scale array processor.

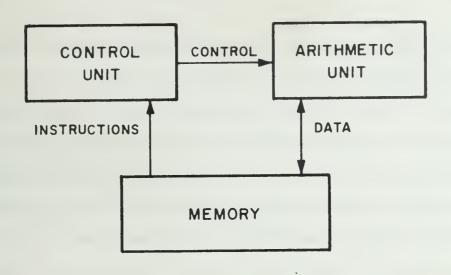

Figure 3-1 contrasts the organization of an array processor with that of a conventional computer. In a conventional machine, control hard-ware (shown in the figure collected into one functional block and labelled the Control Unit) interprets the instruction stream and provides signals which control the operation of the rest of the hardware, collected into the block called the Arithmetic Unit. In most conventional machines, both the instructions and the data are stored in one memory. In most conventional computers, as suggested above, the control and arithmetic - or execution -

Figure 3-1 The Basic Structures of a Classical Computer and an Array Computer

functions are seldom as clearly separated as the figure suggests. In the array computer, however, the control and execution functions are clearly separated. The arithmetic unit is replicated many times (1024 in the SOLOMON (Slotnick, 1962) and 64 in the ILLIAC IV (Slotnick, 1968)), and the data memory is divided so that each of the arithmetic units operates on its own data stream under the control of one common program. In a conventional computer, conditional tests on data values in the single data stream alter the flow of the single instruction stream. In the array processor, residual local control in the processors of the array permits conditional tests on data to allow individual processors to skip executing instructions. In a standard technique for controlling iterations, the control unit samples the activity status of the processors in the array, and stops the iteration when all of them become inactive.

Application studies reported by Kuck (Kuck, 1968) have shown that another local control feature is a vital element in an array processor. The ability of each processor to index a control unit supplied data address permits much more flexible use of the processors in the array. In the general circulation model, processor level indexing is necessary to support the table look up process used in the radiation calculation phase of the model.

Virtually all problems for which array processors are suited require that the processors in the array exchange data values. In the SOLOMON computer, the 1024 processors were arranged in a square thirty-two processors on a side, and each processor could access the memories of its four nearest neighbors in addition to its own. The sixty-four processors

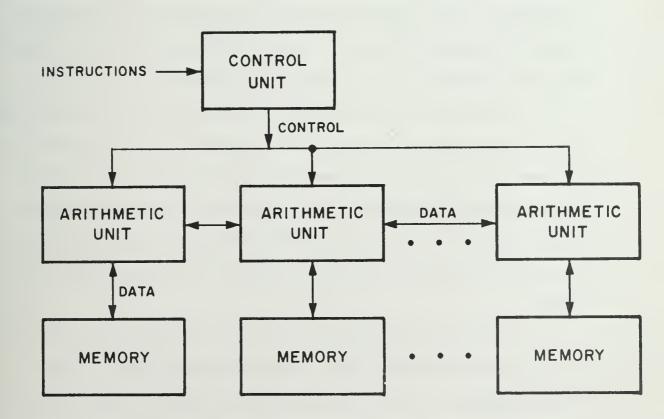

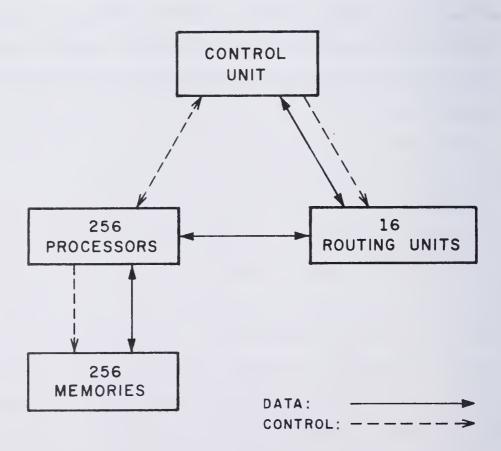

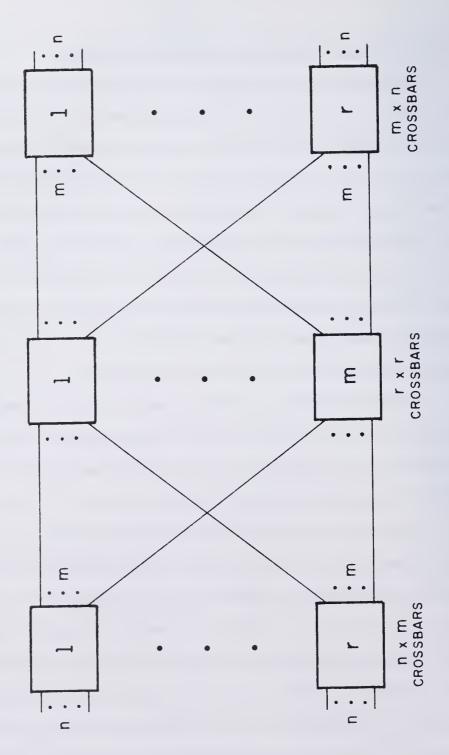

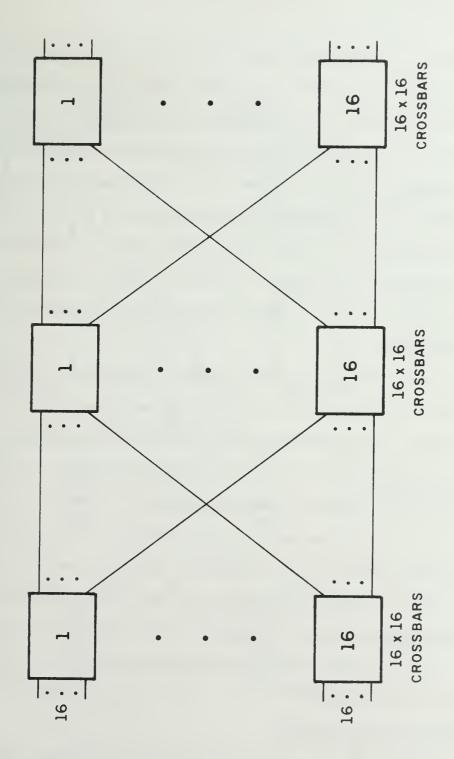

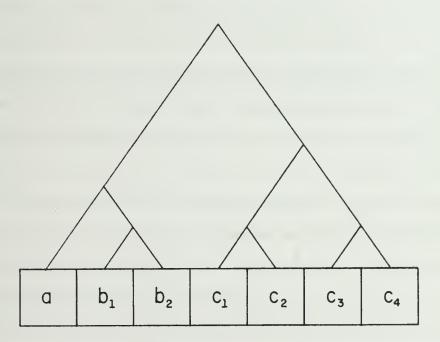

of the ILLIAC IV are also arranged in a square, and each processor can receive values from its nearest four neighbor processors. In the design described in this paper, we use a separate routing network model after the suggestions of Lawrie (Lawrie, 1973) which permits much more flexible interprocessor communication. Figure 3-2 shows the design described in the remainder of this paper in block form. The machine includes a control unit, 256 array processors and their memories, and a sixteen unit three stage routing network.

Figure 3-2 Block Diagram of the System

#### 4. The System Design

The following sections will describe the system design. The initial sections will establish the important parameters of the design. Subsequent sections will discuss the arithmetic processor, routing network, and control unit of the system.

#### 4.1 System Parameters

In this group of sections, the basis for the word length, memory size, and other basic system parameters choices are given.

#### 4.1.1 Word Size

The UCLA and GISS models run in single precision of the IBM System/360 (Arakawa, 1972; Tsang, 1973). Williamson and Washington of the National Center for Atmospheric Research (NCAR) performed precision experiments with the NCAR model (Williamson, 1973). Normally, the CDC machines on which that model runs operate on a forty-eight bit fraction. Through software means, they ran twenty-four and twenty-one bit test cases, and compared the result with a forty-eight bit control runs. They concluded that "the lower-precision arithmetic planned for the next generation of computers [that is, twenty-four bit fractions] does not seriously affect the results from the current NCAR [five degree, six layer] global circulation model." Dr. Larry Gates of the Rand Corporation has recently rescinded his decision to run the Rand modification of the UCLA model in double precision (Gates, 1975). He said that difference between single and double precision test runs are well within the so-called "predictability error" for hydrodynamics calculations discussed by Lorentz (Lorentz, 1963).

On the basis of the above information, we have decided that single precision arithmetic is sufficient for the execution of the model.

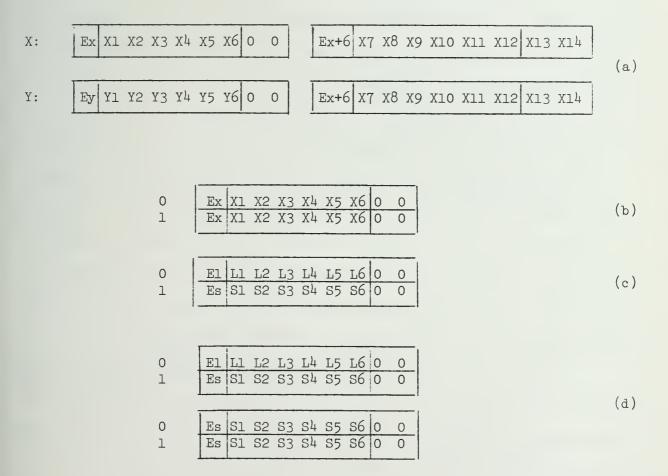

#### 4.1.2 Word Format

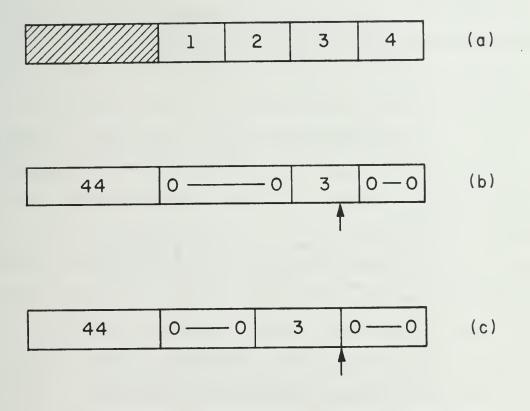

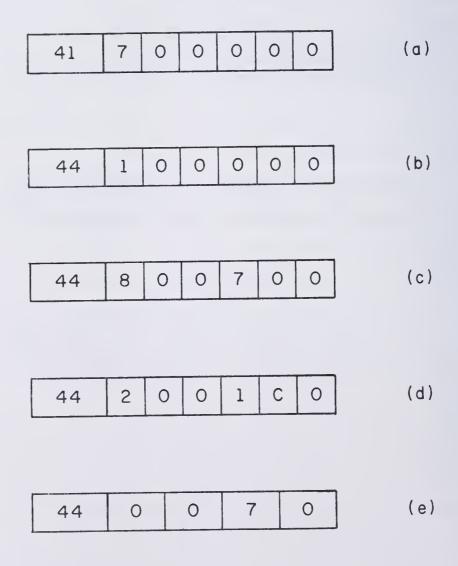

The system was designed to operate in conjunction with IBM series 360 computers at GISS. Data preprocessing steps to prepare input for the system and data post processing steps to analyze the results of experiments will be done on the IBM equipment. Programming for the system is to be in a FORTRAN-like higher level language, so that floating point operation is required. Because of the cooperation required between the system and the 360, it was decided to make the floating point format of the mcahine the same as that of the 360 (IBM, 1970). The floating point format for the design is shown in Figure 4.1.2-1. A floating point word is represented in sign magnitude form by a one bit sign, a seven bit exponent, and a twenty-four bit fraction. A zero sign bit is used for non-negative numbers. The seven bit exponent field contains a biased representation for exponent vlaues between minus sixty-four and plus sixty-three inclusive. The proper representation for an exponent value is found by adding the value to the bias, sixty-four. Thus, for example, an exponent field value of 41 base sixteen represents an exponent value of plus one. The magnitude part ot the number is a proper fraction; that is, the exponent is an implicit binary point at the left of the most significant fraction bit. The exponent field represents the power of sixteen which must multiply the fraction to correctly express the value of the floating point number as a whole. Because the exponent radix is sixteen, a change of one in the exponent value requires a shift of four bit positions in the fraction to represent the same numerical value. Thus, the twenty-four bit fraction can be regarded as a six hexidecimal digit fraction; each hexidecimal digit is represented by four continguous bits of the fraction, and shifts of the fraction are made in multiples of four bit positions.

| S<br>I<br>G<br>N |   | EXPONENT | FRACTION |    |

|------------------|---|----------|----------|----|

| 1                | 2 | 8        | 9        | 32 |

Figure 4.1.2-1 The Floating Point Word Format

### 4.1.3 Memory Requirements

Based on experience with the cost of development of special high data rate disk systems which we obtained with ILLIAC IV, we decided that the memory of the machine should be large enough to contain all of the data. The memory requirement was estimated by running the COMMON for the 360/95 model through the IBM FORTRAN/H compiler. Space for four three dimensional variables (two velocity components, salinity and temperature) and one two dimensional variable (the vertically averaged stream function) of an eventual ocean model was added for the 96 x 128 and 192 x 256 models.

Because that machine would have a program memory separate from its data memory for the processor array, space for the program is not included in the following estimates. Table 4.1.3-1 displays the amount of memory required for several sizes of the model, including the 96 x 128 and 192 x 256 models with oceans.

| words | of | memory   |

|-------|----|----------|

| WOLUS | OI | THEMOT ? |

| NS x EW x Z    | no ocean          | 7 level ocean |

|----------------|-------------------|---------------|

| 82 x 128 x 15  | 1,378,411         |               |

| 96 x 128 x 15  | 1,613,289         | 1,969,641     |

| 128 x 200 x 15 | 3,358,601         |               |

| 256 x 401 x 15 | 13,457,305        |               |

| 164 x 256 x 15 | <b>5,506,1</b> 25 |               |

| 192 x 256 x 15 | 6,445,385         | 7,870,793     |

Table 4.1.3-1

The machine should be built with  $2^{23}$  words of memory to accommodate the 192 x 256 grid. Each of the 256 processor memories would have  $2^{15}$  (or 32768) words. Each of these words will contain thirty-two information bits

and six Hamming code bits (Hamming, 1950) for detection and correction of single bit errors. The decision to include error detection and correction hardware was taken on the advice of the staff of the University of Illinois Physics department. They have constructed semi-conductor memory for their computer, and found that the error detection and correction bits which they included were well worth while, both in terms of improved system operation and increased maintainability (Downing, 1974).

#### 4.1.4 Measurements of the GISS Model

To discover the relative importance of multiplication and the frequency of double precision operations in the execution of the model, the GISS model was run for one time step on the University of Illinois' 370/158 under the control and observation of a program which computes the frequencies of all instructions executed by the program it observes. A series of runs was made to permit instruction counts for the important parts of the model to be determined. Execution times for these parts of the model were determined by the GISS staff (Karn, 1974) during a one man year effort which produced an ILLIAC IV version of the GISS model. Table 4.1.4-1 shows the number of instructions executed in each of three parts of the model, the 360/95 time for execution of those parts, and the instruction processing rate of the 360/95. Table 4.1.4-2 gives the frequencies for single and double precision floating point multiplications and divisions in the parts of the model.

Approximately half of the instructions executed were floating point instructions. These were nearly equally divided between addition and subtraction on one hand and multiplication and division on the other. The

| Part of the Model | Instructions | 360/95 Time | 360/95 Rate |

|-------------------|--------------|-------------|-------------|

| Initialization    | 11,891,631   |             |             |

| COMP1-COMP2       | 69,480,878   | 10.3 sec.   | 6.75 MIPS   |

| COMP3             | 43,505,137   | 6.54 sec.   | 6.65 MIPS   |

Table 4.1.4-1 Measurement Values

| 360 Instruction | Initialization | COMP1-COMP2 | COMP3     |

|-----------------|----------------|-------------|-----------|

| MDR             | 1              | 423,936     | 132,480   |

| MD              | 330            | 16          | 103,765   |

| MER             | 756            | 2,221,358   | 823,153   |

| ME              | 2,134          | 4,022,947   | 2,056,291 |

|                 |                |             |           |

| DDR             | 3              | 105,984     | 33,120    |

| DD              | 1              | 0           | 0         |

| DER             | 77             | 359,584     | 615,025   |

| DE              | 1,773          | 440,950     | 929,372   |

|                 |                |             |           |

Table 4.1.4-2 Instruction Counts

ratio of multiplications to divisions (weighting COMP1-COMP2 by six to account for the more frequent use of these routines in normal model execution) is 6.15 multiplications to one division. The vast majority of the double precision floating point operation are performed by one assembly language subroutine which raises a number to a constant power. This routine uses double precision because the speed of single and double precision operations on the IBM 360/95 is the same. An approximation formula with a few more terms can be used without requiring any double precision.

On the basis of the above information, we decided to design a single precision processor whose floating point addition and multiplication times are comparable. Double precision operations will be performed on the single precision hardware of the design relatively slowly since they occur with such low frequency.

#### 4.1.5 Processor Speed Requirements

The system is to have roughly one hundred times the processing capability of the IBM 360/95 for the weather model. As we saw in section 4.1.4, the 360/95 executes approximately 6.7 (10)<sup>6</sup> operations per second on the GISS general circulation model. We have already decided that the machine we design will be an array processor with an architecture similar to that of ILLIAC IV. How many processors should the machine have? To achieve 6.7(10)<sup>8</sup> operations per second, a 256 processor machine must perform one operation in 382 nano-seconds; a 512 processor machine need only perform one operation in 764 nano-seconds. On the other hand, as we will see in section 4.3 - which discusses the routing network - it is important to have the number of processors be a perfect square: 256 is the

square of sixteen, but 512 is not a perfect square. Moreover, a 256 processor machine will be more reliable and have a higher availability than a similar 512 processor machine. Therefore, we will design a machine with 256 processors. We would, therefore, like the operation time for a processor to be on the order of 400 nano-seconds.

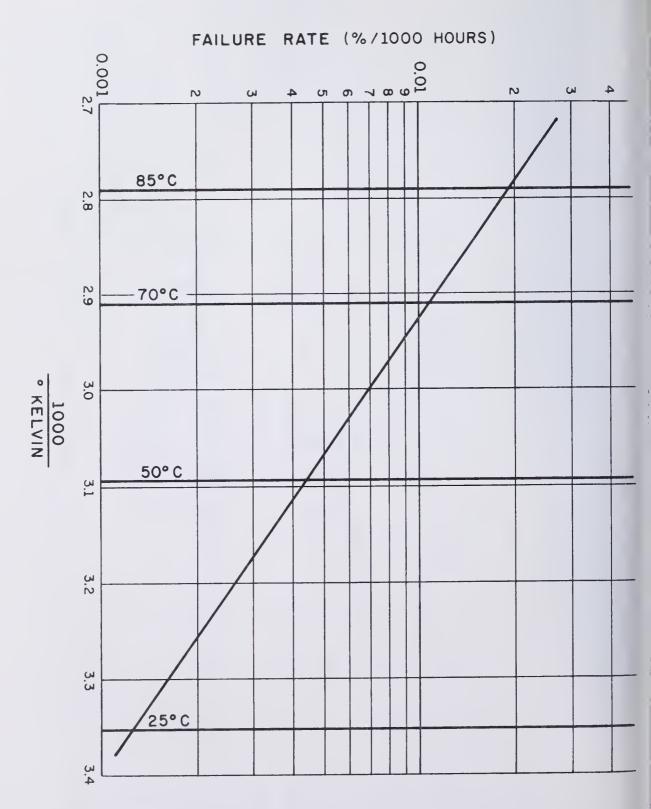

## 4.1.6 The Choice of TTL Technology for the Processor

It was clear from the outset that the time and budget constraints on the design necessitated using an existing integrated circuit technology, and in fact a family which is currently commercially available "off the shelf". The choice must be either TTL, MOS, or ECL (Hnatek, 1973). A higher level of integration (that is, more powerful individual packages is avalable in the TTL family than is available in the ECL family. Moreover, the new Schottky variant of TTL logic is nearly as fast as ECL. The speed of MOS logic is far slower than that of even standard TTL. A floating point processor with a fast multiplier will surely require using several hundred integrated circuits in its design. Fewer high level packages are required than low level packages to achieve the same functions, and package savings pay off in both board and interconnection savings. Therefore, we chose to design the processor in terms of TTL integrated circuits.

Package savings in the processor design result from the use of two different package interconnection properties of two different special forms of TTL logic. These are discussed in the following two sections.

# 4.1.6.1 Open Collector Logic and the Wire AND

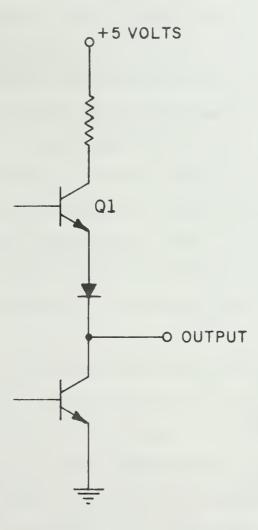

A standard TTL output stage is shown in Figure 4.1.6.1-1. The active pull-up provided by transistor Ql is that it permits faster operation

Figure 4.1.6.1-1 The Standard TTL Totem Pole Active Pull-up Output Stage

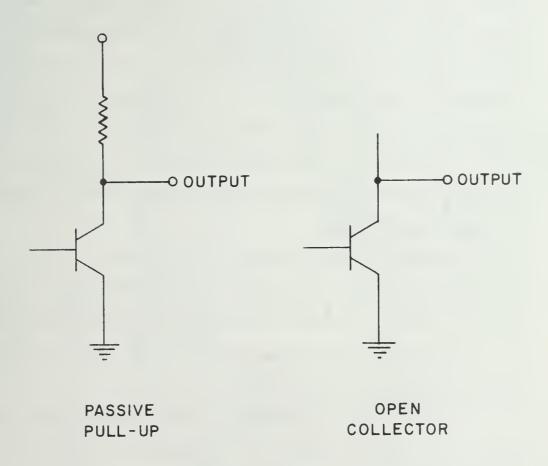

than that of the resistor-transistor (RTL) or diode-transistor (DTL) families from which the TTL family evolved. The passive output stage of Figure 4.1.6.1-2 of the DTL family is used in some of the slower of the TTL integrated circuits. Deletion of the pull-up resistor of the passive output stage results in the so-called output collector output. Open collector outputs of several packages can be wired together through a common external pull-up resistor. If all of the output signals so wired together are logic ones, each circuit will source less than one milliamp so the resulting current flow for the entire collection of wire ANDed circuits results in a logic one. However, if one or more of the wire ANDed output signals is a logic zero, the corresponding circuits will sink on the order of forty milliamps, so that the resulting voltage level of the ensemble falls to that of a logic zero.

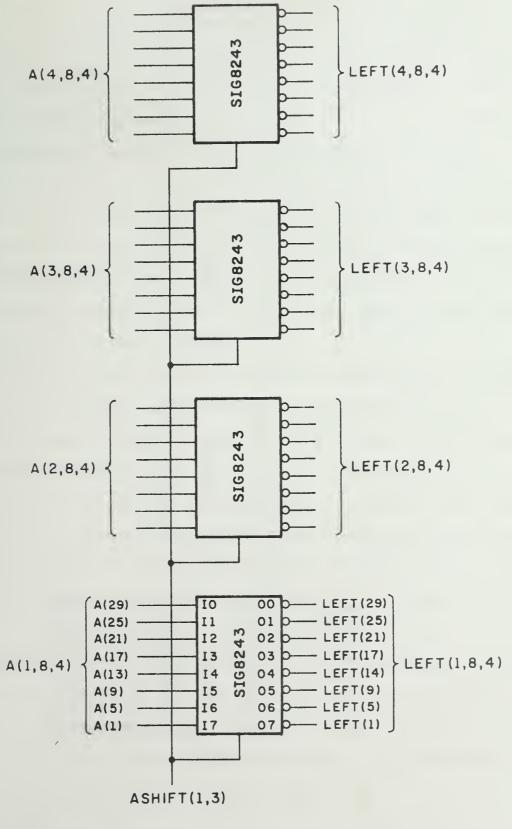

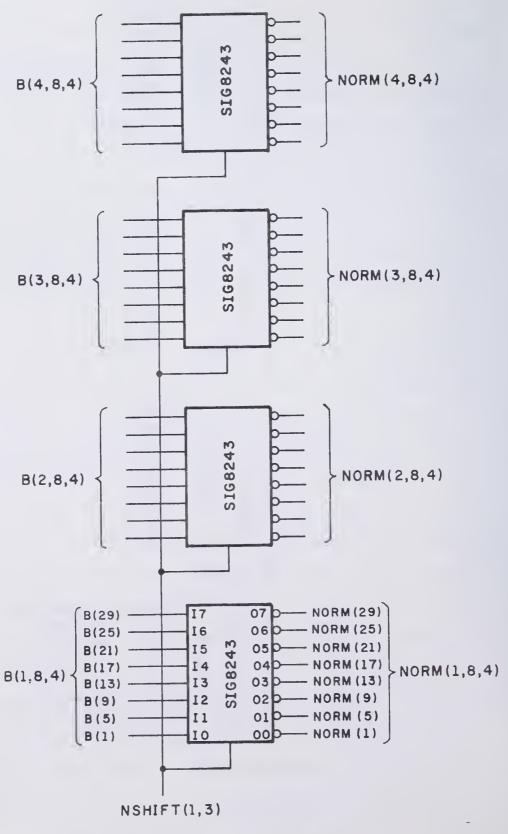

Within the processor, the open collector outputs of the Signetics 8243 eight position scalers used in the right operand alignment shift logic and the normalization left shift logic are wire ANDed together. An enable signal for the device permits forcing all eight output signals to logic ones regardless of the state of the eight input signals. One of the two shift networks is enabled at a time, so that its output bits, ANDed with ones of the disabled device, determine the net output of the ensemble.

## 4.1.6.2 Tri-state Logic and the Wire OR

The National Semiconductor Corporation holds the patents for another output control technique which they refer to by the registered trademark "tri-state" logic. Standard TTL circuits augmented by the National technique have an enabling input which can be used to force the

Figure 4.1.6.1-2 TTL Passive Pull-up and Open Collector Output Stage

outputs of the device to a high impedance state (Hnatek, 1973). The output impedance of a standard TTL output is nominally fifty ohms. The output impedance of a disabled tri-state output is nominally 50,000 ohms. Thus, if several tri-state outputs are wired together and all but one of them are disabled, the current into or out of the disabled outputs is negligible compared to that for the one enabled output. Up to one hundred or more tri-state outputs can be wired together on a single bus. The resulting wired connection is usually referred to as a wired OR, and its logic state is determined by the logic state of the enabled output.

The processor design makes extensive use of tri-state devices to reduce the need for selectors between otherwise competing signals.

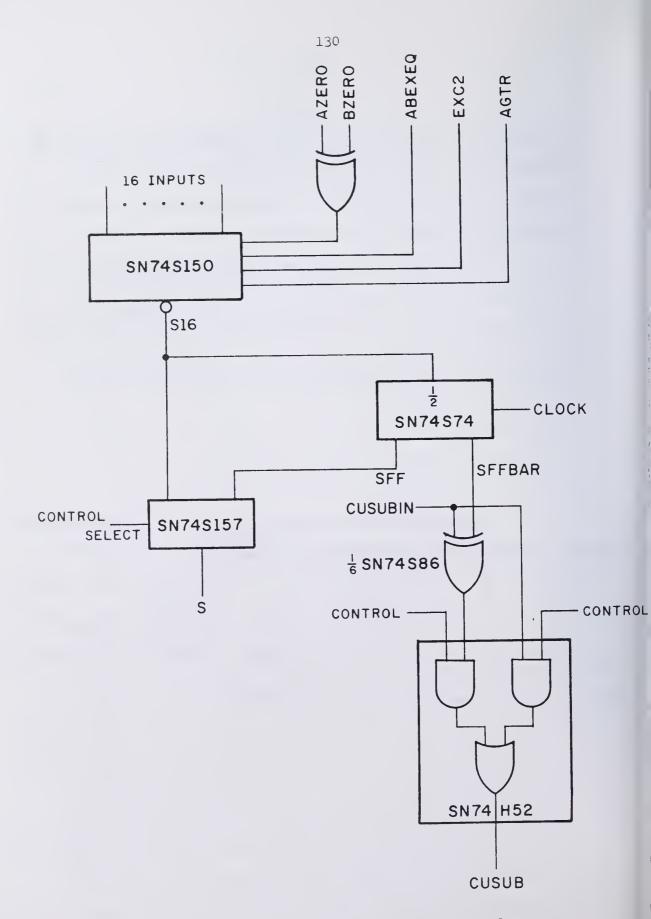

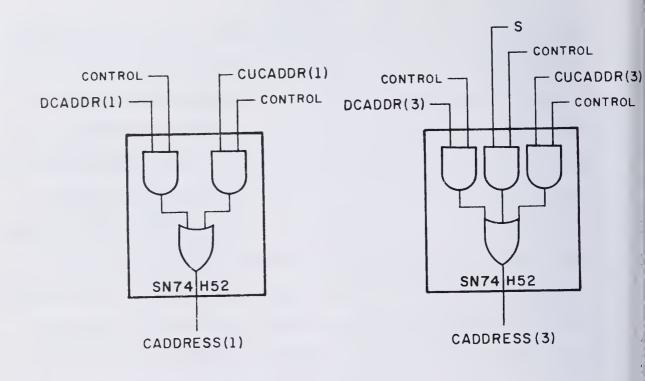

4.2 The Processor Design

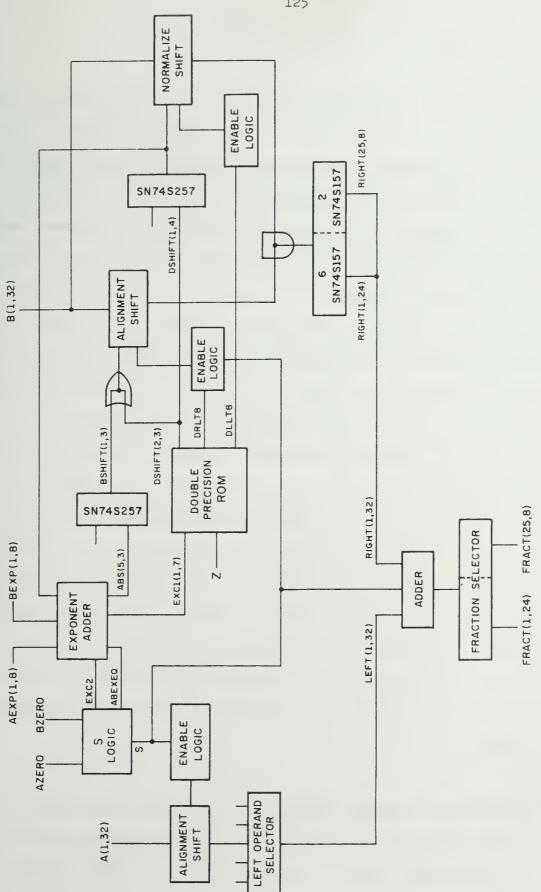

A simplified block diagram of the processor is shown in Figure 4.2-1. The names in the blocks of this figure (with the exception of the 2/1 Selector blocks) are the names of the Figure or Figures which present the logic of that block in more detail. Each of these blocks is described in detail in the following sections.

Multiplication is performed by logic external to that shown in Figure 4.2-1. The two twenty-four bit operands to be multiplied are sent to the multiplier as shown, and both the most and least significant halves of the product are returned. See section 4.2.5.2.4 and (Stenzel, 1975) for a detailed description of the multiplier.

The processor as a whole is a large combinatorial circuit which is conditioned by control signals from the control unit. It operates in steps governed by one clock pulse. A typical cycle begins with operand selection.

Figure 4.2-1 Block Diagram of the Processor

Two operands, one of which may come from memory, flow through the paths in the logic selected by the set of control signals. At the completion of a cycle, result values are clocked into the registers specified by the set of control signals.

In any logic design, options are available at many stages. The rules governing the choice among options in this design can be qualitively stated as follows: minimize cost and package count, but not at the expense of time in the critical path. Cost is reflected not only in the direct cost of the packages, but also by the amount of board area (and hence the number of boards) which the packages occupy. Minimizing the number of boards can lower overall cost by reducing the need for backplane wiring or mother boards and eliminate the need for inter-board connections. The board area for a package was assumed to be proportional to the number of pins which the package has. Although this assumption is not strictly true, it serves well as an operation rule of thumb when making design choices.

# 4.2.1 Conventions Used in the Figures Which Describe Logic

Designing computer hardware in terms of existing integrated circuit packages differs from computer design in terms of discrete components. In many cases, the designer working with integrated circuits finds that no existing package exactly suits the need of the moment. What he must then do is make the best compromise he can with the packages which are available, according to the general guidelines which he has adopted.

The simplest example of the above general comment is that it often happens that an N-input gate of some type is needed. A concrete example in this design is that a four input OR gate is needed by the logical demands of the function to be implemented. What are available are two input OR gates

and two, four, and five input NOR gates. Among these gates, only - the five input NOR gate - is available in Schottky form. When the desired logic function is in a time-critical path, the highest speed element should be used. Hence, one finds himself using a five input gate for a four input function. Many instances of such use occur in this design. When they occur in the figures, only the number of inputs which are required for the logic function being implemented are shown. The extra leads which may exist are assumed to be connected to sources of logic ones or zeros as necessary. For example, the extra input of the above five input NOR gate would have to be connected to a constant logic zero source to guarantee the correct operation of the logic in which it is used.

Detailed documentation for the integrated circuits used in this design can be found in four industry data books. In the description which follows, the following notation given in Table 4.2.1-1 was used for naming components.

| Form of the Name | Source for Detailed Information                                                                                                    |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SN74xxxx         | The TTL Data Book for Design Engineers, First Edition, Document Number CC-411, Texas Instruments Incorporated, 1973.               |  |  |

|                  | Supplement to the TTL Data Book for Design Engineers, First Edition, Document Number CC-416. Texas Instruments Incorporated, 1974. |  |  |

| SIGxxxx          | Signetics Digital, Linear, MOS Data Book, Signetics Corporation, $197^{l_1}$ .                                                     |  |  |

| AMxxxx           | Advanced Micro Devices Data Book, Advanced Micro Devices Incorporated, 1974.                                                       |  |  |

| NATxxxx          | Digital Integrated Circuits, National Semiconductor Corporation, 1974.                                                             |  |  |

Table 4.2.1-1 The Notation for Package Names in the Logic Design Figures

### 4.2.2 Signal Name Notation Used in the Design Description

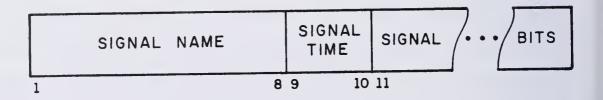

In the description of the design in the follwoing sections, signals will be named by an identifier of eight or less capital letters and digits. The first character of a signal name will be a letter. Multi-bit signals are named by a single identifier to which bit specifications are appended. A bit specification is a list of up to three integers separated by commas and enclosed in parentheses. The bits of multi-bit signals are numbered from one for the most significant to N for the least significant bit of an N bit signal. A bit specification which consists of a single integer specifies the single bit of the multi-bit signal with that integer as its bit number. In a bit specification with two integers, the first specifies the bit number of the most significant bit of the signal and the second specifies the number of contiguous bits in the signal. The third integer of a three integer bit specification is the difference between successive bit numbers in the specified signal. Table 4.2.2-1 gives several examples of signal names.

| Signal Name | Meaning                                               |

|-------------|-------------------------------------------------------|

| A           | the one bit signal A                                  |

| B(3)        | bit three of the multi-bit signal B                   |

| B(1,32)     | bits one through thirty-two of the multi-bit signal B |

| B(5,4)      | bits five through eight of the multi-bit signal B     |

| c(1,2,4)    | bits one and five of the multi-bit signal C           |

Table 4.2.2-1 Several Examples of Signal Names

This notation for signal names is used consistantly throughout the text and figures which describe the design. It is also used for signal names in the input language for the logic simulation package described in section 5.1. In the truth tables which follow, a lower case "x" signifies that the package described by the truth table operate correctly for any value of the signal represented by the "x".

#### 4.2.3 Inversion in the Logic Figures

When the function of an integrated circuit includes the logical complement of the inputs, this is shown by a small circle external to the rectangle which represents the integrated circuit. The alignment shift blocks of Figure 4.2-1 are an example of an inverting block.

## 4.2.4 Detailed Description of Two Packages

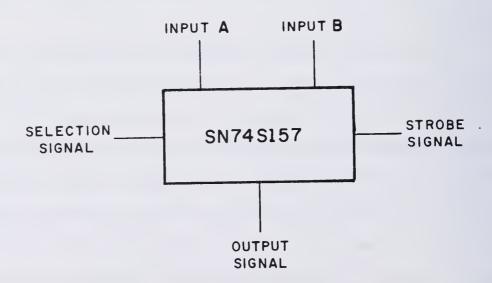

Two packages, the Texas Instruments SN74S157 and the Signetics 8263, are described in detail in this section. Two reasons motivate these detailed descriptions. First, these packages are typical of most of the integrated circuits which are used in this design. Second, and perhaps more important, these particular packages perform critical functions in the design. All of their features are exercised, so that a full understanding of the design is impossible without a full understanding of these two packages.

## 4.2.4.1 The Texas Instruments SN74S157

The Texas Instruments SN74S157 is a quadruple two-to-one selector. It accepts two four bit input operands and a one bit selection signal and produces a four bit output. The output is the four bit input designated by the selection signal. There is one more input, however. A one bit strobe signal can be used to force the outputs to zeros without regard to the input

signals. There are several occasions in the design where the strobe signal is used to good advantage. The truth table for the SN74S157 is given in Table 4.2.4.1-1.

|        |        | Output    |        |        |

|--------|--------|-----------|--------|--------|

| Dat    | a      | Selection | Strobe | output |

| х      | х      | х         | 1      | 0      |

| A(1,4) |        | 0         | 0      | A(1,4) |

| х      | B(1,4) | 1         | 0      | в(1,4) |

Table 4.2.4.1-1 The Truth Table for the Texas Instruments SN74S157

## 4.2.4.2. The Signetics 8263

The Signetics 8263 is a quadruple three-to-one selector. It accepts three four bit input operands, a two bit selection signal, and a one bit complement signal, and produces a four bit output. The output is the four bit input designated by the selection signal. The two bit selection signal can specify one of four input signals; the fourth state is used to set the output to zero without regard to any of the input signals. The complement signal can be used to specify that the output is to be the logical complement of the selected input. The truth table for the Signetics 8263 is given in Table 4.2.4.2-1.

|        | Inputs |        |    |            |        |  |  |

|--------|--------|--------|----|------------|--------|--|--|

|        | Data   |        |    | Complement | Output |  |  |

| X      | Х      | Х      | 00 | 0          | 0000   |  |  |

| A(1,4) | X      | Х      | 01 | 0          | A(1,4) |  |  |

| X      | B(1,4) | Х      | 10 | 0          | B(1,4) |  |  |

| X      | X      | C(1,4) | 11 | 0          | C(1,4) |  |  |

| X      | X      | Х      | 00 | 1          | 1111   |  |  |

| A(1,4) | Х      | Х      | 01 | 1          | A(1,4) |  |  |

| Х      | B(1,4) | Х      | 10 | 1          | B(1,4) |  |  |

| Х      | Х      | C(1,4) | 11 | 1          | C(1,4) |  |  |

|        |        |        |    |            |        |  |  |

Table 4.2.4.2-1 The Truth Table for the Signetics 8263

## 4.2.5 The Processor Design

In the two sections which follow, the design of the processor is completely described. The first of these sections describes functional logic blocks in their own right without regard to the contributions which those blocks make in the operation of the processor. The second section describes how the processor performs normalization, rounding, floating point addition/subtraction, floating point double precision addition/subtraction, floating point multiplication, and finally floating point division. This section relies on an understanding of the former sections describing the various logic blocks. It describes the control logic which is necessary to integrate the operation of those logic blocks to perform the desired operations.

#### 4.2.5.1 Logic Blocks

The following sections describe several logic elements which perform definite functions in support of larger operations in the processor.

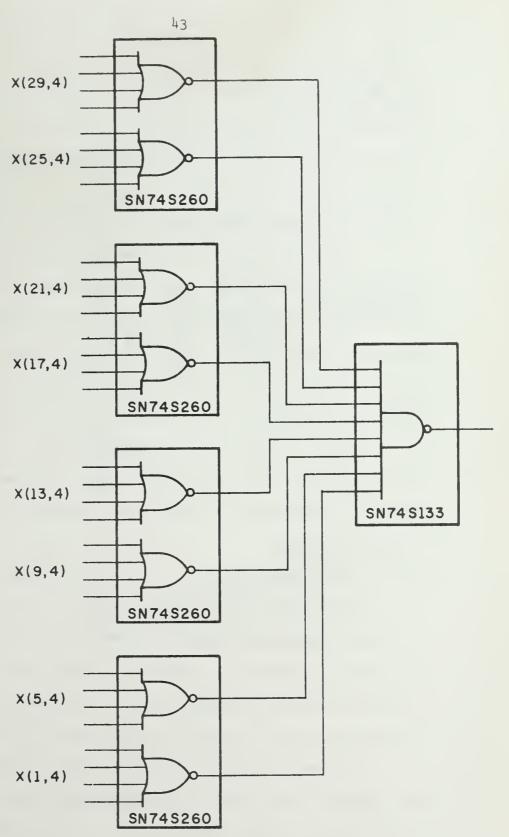

4.2.5.1.1 The Zero Detect Logic

A zero detect logic block produces the logical OR of thirty-two bits. Three instances of the zero detect block occur. In all three cases, the thirty-two input bits constitute a thirty-two bit operand fraction. Figure 4.2.5.1.1-1 depicts the zero detect logic. The packages used are four SN74S260 dual five-input positive NOR gates and one SN74S133 thirteen-input positive NAND gate. Each of the NOR gates is used to produce the NOR of four input fraction bits. The eight results are combined by the NAND gate to yield the desired OR of the thirty-two input bits.

In Figure 4.2.5.1.1-1, the four bit groups shown as inputs to the NOR gates represent four bit digits of a fraction. In only one of the three

Figure 4.2.5.1.1-1 The Zero Detect Logic

instances of the zero detect logic is this rigid connection scheme necessary. (See section 4.2.5.2.1 Normalization.) In the other two cases, the total of forty NOR gate inputs can be connected in whatever manner is convenient for circuit board routing purposes.

## 4.2.5.1.2 The Fraction Comparator

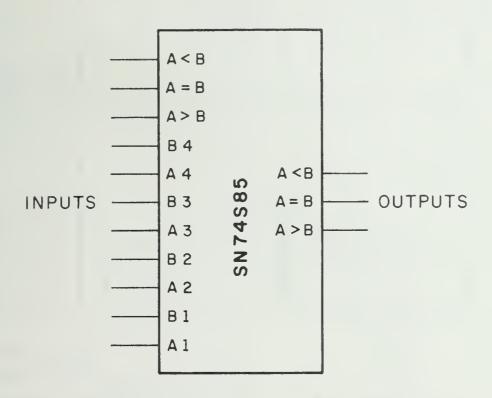

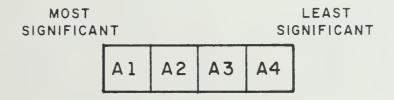

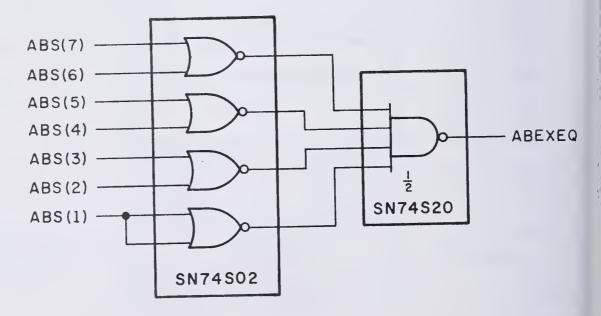

This logic block is built entirely with the SN74S85 four bit comparator. This integrated circuit accepts a pair of four bit operands and three signals which permit fabrication of multi-bit comparators and produces three one bit output signals. Figure 4.2.5.1.2-1 shows one SN74S85, and illustrates how it is used in this design. Table 4.2.5.1.2-1 is the truth table for the SN74S85. Figure 4.2.5.1.2-2 shows how eight SN74S85's are used to compare two thirty-two bit fraction values. The output signal AGTR is a logic one if and only if the A(1,32) input signal exceeds the B(1,32) input signal. The ABEQ signal is a logic one if and only if the input signal values are identically equal.

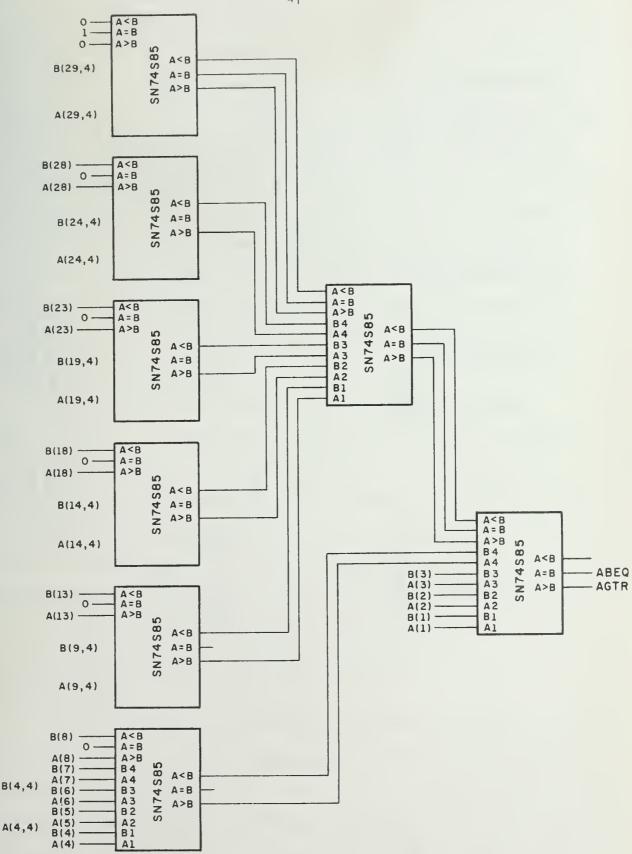

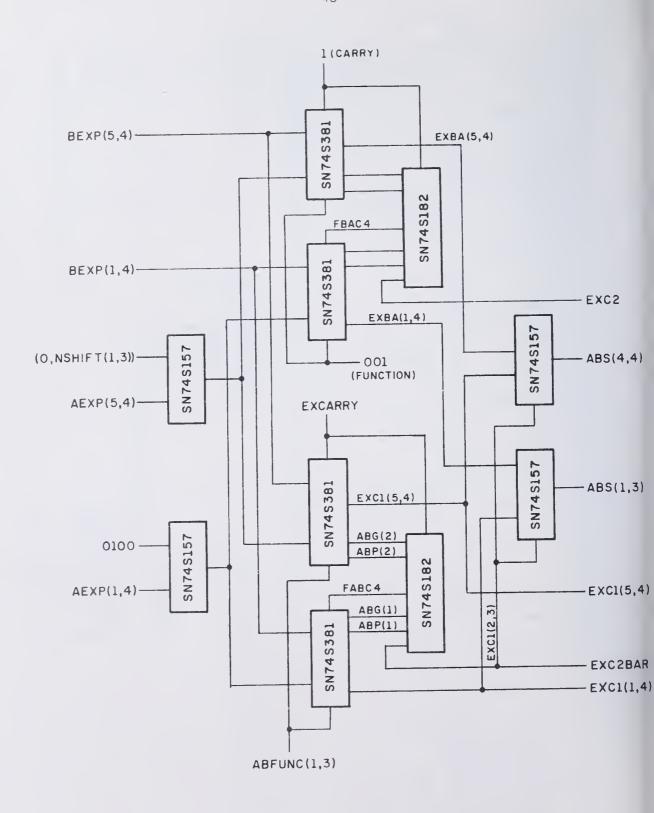

## 4.2.5.1.3 The Exponent Adder

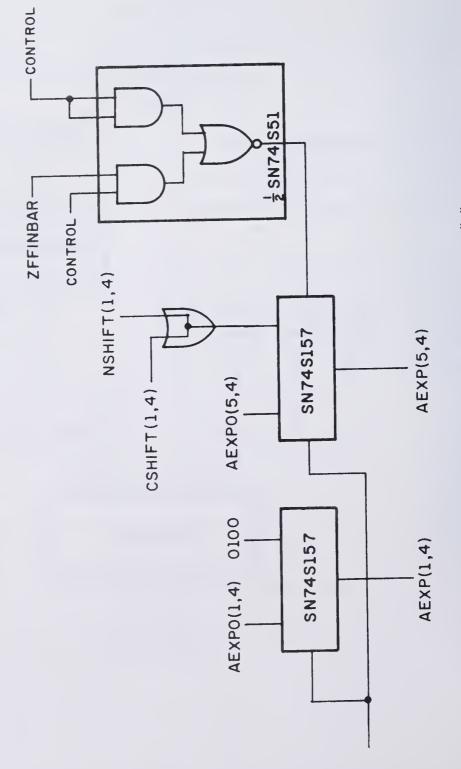

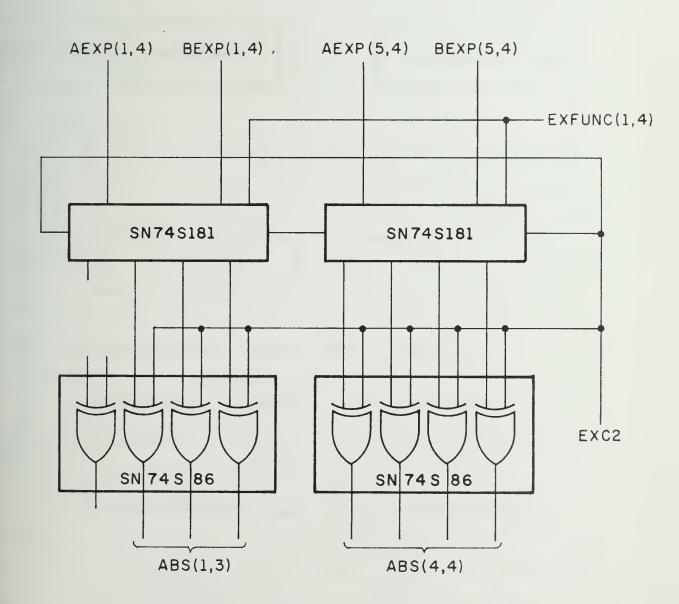

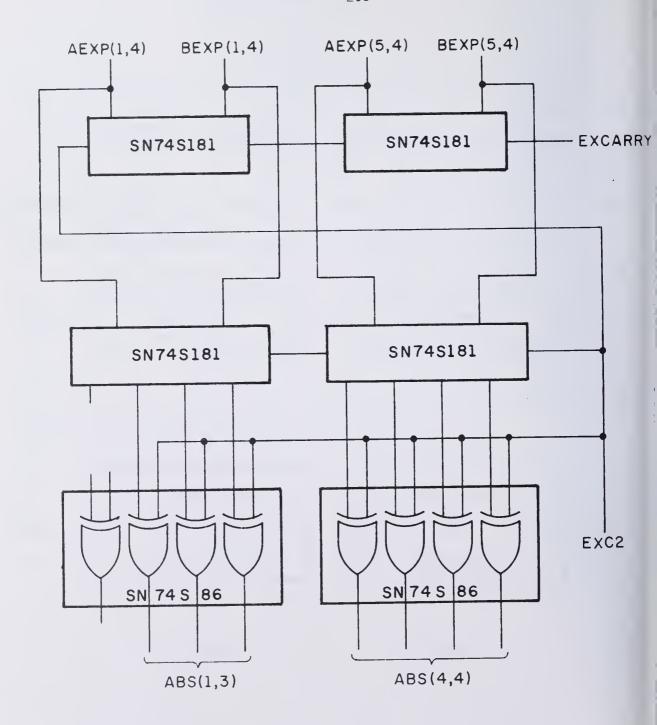

The exponent adder, shown in Figure 4.2.5.1.3-1, accepts two eight bit exponent quantities, AEXP(1,8) and BEXP(1,8), one three bit function specification, ABFUNC(1,3), and a one bit input carry signal, EXCARRY. The two eight bit exponent inputs consist of a zero bit as most significant bit, followed by the seven bits of the biased exponent for the two operands.

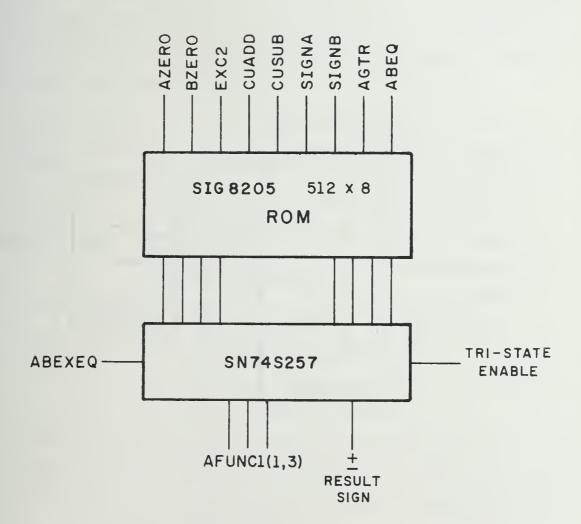

The exponent adder produces the eight bit combination of the two input exponents, EXCl(1,8), as specified by the function, ABFUNC(1,3), the absolute value of the difference of the two input exponents, ABS(1,7), and two one bit control signals, EXC2 and EXC2BAR.

Figure 4.2.5.1.2-1 The SN74S85 Four Bit Comparator

| Relation of the   | Casca | ading In | puts  | Outputs |       |       |

|-------------------|-------|----------|-------|---------|-------|-------|

| 4 bit data inputs | A = B | A < B    | A > B | A = B   | A < B | A > B |

|                   |       |          |       |         |       |       |

| A > B             | X     | X        | Х     | 0       | 0     | 1     |

| A < B             | X     | X        | Х     | 0       | 1     | 0     |

|                   |       |          |       |         |       |       |

| A = B             | 1     | X        | Х     | 0       | 1     | 0     |

|                   | 0     | 0        | 0     | 0       | 1     | 1     |

|                   | 0     | 0        | 1     | 0       | 0     | 1     |

|                   | 0     | 1        | 0     | 0       | 1     | 0     |

|                   | 0     | 1        | 1     | 0       | 0     | 0     |

|                   |       |          |       |         |       |       |

Table 4.2.5.1.2-1 The Truth Table of the SN74S85 Four Bit Comparator

Figure 4.2.5.1.2-2 The Fraction Comparator

Figure 4.2.5.1.3-1 The Exponent Adder

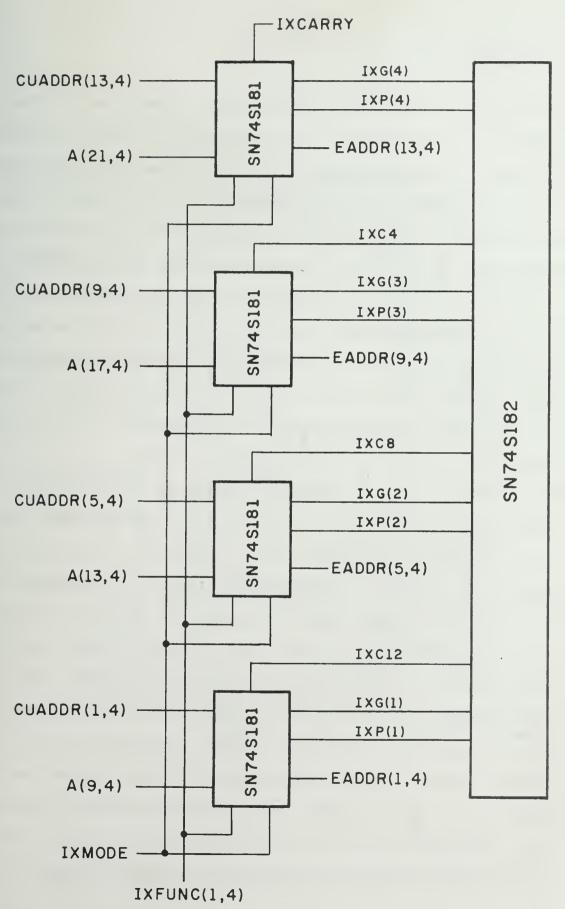

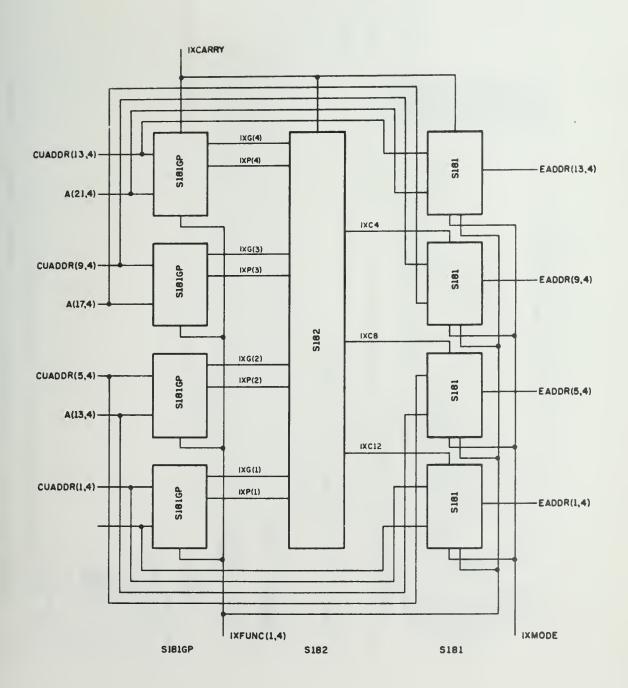

The main functional component of the exponent adder is the SN74S381 arithmetic-logic unit. The functions performed by the SN74S381, together with the function codes which specify them, are shown in Table 4.2.5.1.3-1 (Texas Instruments Corporation, 1974). The SN74S381 does not produce an output carry signal. Instead, it produces the standard pair of carry look ahead singals for the two four bit operands. One of these signals indicates whether the two input operands will generate a carry; the other signal indicates whether an input carry of one will be propagated (Ledley, 1960). The generate and propagate signals must be used in conjunction with a carry generator such as SN74S182 (Texas Instruments Corporation, 1973).

The exponent adder actually consists of two eight bit adders working in parallel. The one shown at the top of Figure 4.2.5.1.3-1 always computes the difference A(1,8) - B(1,8). The lower adder computes the function specified by the control unit signals ABFUNC(1,3) and EXCARRY. When ABFUNC(1,3)=010, and EXCARRY=1, ABS(1,7) is the absolute value of the exponent difference and EXC2 and EXC2BAR have the meanings given in Table 4.2.5.1.3-2. The absolute value is computed by computing both A(1,8) - B(1,8) and B(1,8) - A(1,8), and selecting the positive result with the pair of SN74S157 two-to-one selectors by using EXC2BAR as the selection signal.

### 4.2.5.1.4 Shifting

Fraction alignment shifting and the normalization shifting are both accomplished by using the Signetics 8243 eight bit position scaler (Signetics Corporation, 1974, pp. 3.28 through 3.32). This device has open collector outputs so that several can be wire ANDed together. The shifted output bits are the logic complements of their corresponding input bits. When disabled,

|        | Input  | Output   |       |                     |

|--------|--------|----------|-------|---------------------|

| A(1,4) | B(1,4) | Function | Carry | Outoput             |

| Х -    | Х      | 000      | X     | 0000                |

| A(1,4) | B(1,4) | 001      | 0     | B(1,4) - A(1,4) - 1 |

| A(1,4) | B(1,4) | 001      | 1     | B(1,4) - A(1,4)     |

| A(1,4) | B(1,4) | 010      | 0     | A(1,4) - B(1,4) - 1 |

| A(1,4) | B(1,4) | 010      | 1     | A(1,4) - B(1,4)     |

| A(1,4) | B(1,4) | 011      | 0     | A(1,4) + B(1,4)     |

| A(1,4) | в(1,4) | 011      | 1     | A(1,4) + B(1,4) + 1 |

| A(1,4) | в(1,4) | 100      | Х     | A(1,4) (+) B(1,4)   |

| A(1,4) | B(1,4) | 101      | Х     | A(1,4) OR B(1,4)    |

| A(1,4) | B(1,4) | 110      | Х     | A(1,4) AND B(1,4)   |

| X      | X      | 111      | X     | 1111                |

|        |        |          |       |                     |

Table 4.2.5.1.3-1 Functions of the SN74S381 with Active High Carry and Data

| Signal  | Value | Meaning              |

|---------|-------|----------------------|

| EXC2    | 0     | A(1,8) > B(1,8)      |

|         | 1     | $A(1,8) \leq B(1,8)$ |

| EXC2BAR | 0     | $A(1,8) \leq B(1,8)$ |

|         | 1     | A(1,8) > B(1,8)      |

Table 4.2.5.1.3-2 The Meanings of EXC2 and EXC2BAR

the device emits logic ones. Output bits which, because of the specified shift, have no corresponding input bits are also logic ones.

Because the exponent base of the floating point system used in this design is sixteen, alignment and normalization shifting always require a shift by a multiple of four bit positions. The alignment shift logic, Figure 4.2.5.1.4-1, and the normalization shift logic, Figure 4.2.5.1.4-2, can therefore be implemented by using only four SIG8243's each. Each of the scalers accepts one bit from the same position within each of the eight digits of the thirty-two bit fraction to be shifted. The shift amount for each is the number of digit positions to shift.

Although the SIG8243 has both an enable and an inhibit input to control the output state, this design uses only the inhibit signal. When the inhibit signal is a logic one, the output bits are all logic ones. Disabled outputs are used to provide zero operands when the shift amount exceeds seven, and also for several other cases in the design where zero operands are needed. The details of alignment shift control are given in section 4.2.5.2.3 which discusses floating point addition and subtraction Normalization shift control is discussed in section 4.2.5.2.7 on double precision addition and subtraction. When the inhibit signal is a logic zero, shifting of the input bits takes place as specified by the three bit shift select signal.

The device performs shifts in only one direction. Both left and right shifts can be implemented by proper use of the scaler as shown in Figure 4.2.5.1.4-1 and Figure 4.2.5.1.4-2 by altering the orientation of the device with respect to the most significant bit of the input signal.

Figure 4.2.5.1.4-1 The Alignment Shifter

Figure 4.2.5.1.4-2 The Normalization Shifter

#### 4.2.5.1.5 The Left Operand Selection Logic

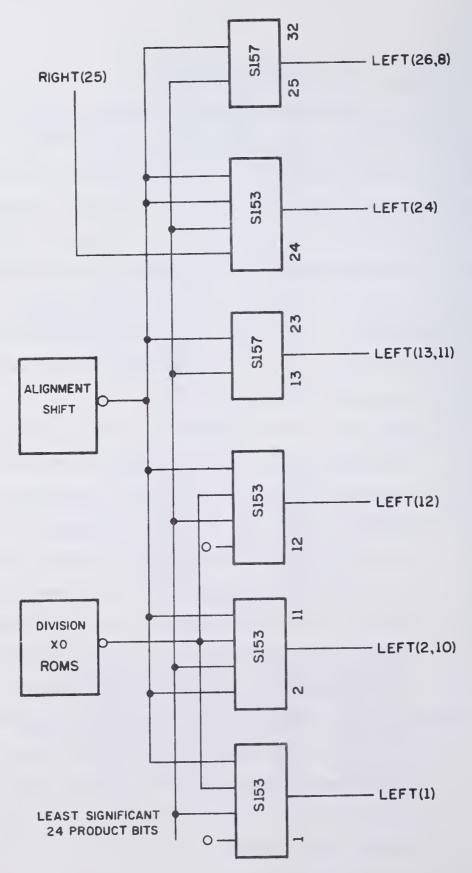

The left operand selector logic block supplies the left operand to the adder. Two different integrated circuits are used in the left operand selector: the SN74S157 quadruple two-to-one data selector and the SN74S153 dual four-to-one data selector. For clarity of description, the blocks in Figure 4.2.5.1.5-1 do not correspond to the above integrated circuit packages, but rather to the selection functions they perform. They are labelled S157 for the two-to-one function, and S153 for the four-to-one function. Whereas the SN74S153 operates on pairs of four bits, the S153 at the bottom of the figure is shown operating on a single four bit group; the S153 next to the bottom operates on ten four bit groups.

The left operand selector supplies six different operands. They are

- 1. the fraction output of the left alignment shift logic

- 2. the twelve high order bits of the first approximation to the reciprocal for division. The other twenty bits of the fraction are forced to one by disabling the left alignment shift logic. As noted above, the alignment shift logic produces complemented outputs, so that the adder operates on active low data. Thus, the ROM which supplies the initial reciprocal approximation must be programmed to supply active low data also.

- 3. the constant fraction one-half (in active low data form) for use in the division algorithm. The high order bit, LEFT(1), is forced to zero by the bottom S153 of Figure 4.2.5.1.5-1, and the other thirty-one bits are forced to one by a disabled alignment shift network.

Figure 4.2.5.1.5-1 The Left Operand Selection Logic

- 4. the constant fraction 2<sup>-12</sup> for use in the division algorithm.

The bit LEFT(12) is forced to zero by the corresponding S153,

and the other thirty-one bits are forced to one by a disabled alignment shift network.

- 5. a value for rounding data values to memory length (twenty-four fraction bits). All bits of this constant are ones from a disabled alignment shift network, except for LEFT(24), which is equal to bit twenty-five of the fraction being rounded.

- 6. the twenty-four least significant bits of a product. The adder normally operates on active low data, and a logic complement follows the adder. A product return in active high data form. If the least significant part of the product is sought, it is complemented by the adder by using the exclusive OR function with ones forming the disabled right alighnment shift logic.

Since the logic for the left operand selector requires the S153 function on a total of thirteen bits and the S157 function on nineteen bits, seven SN74S153 and five SN74S157 integrated circuits are required to implement it. No control local to the processor is necessary for its operation.

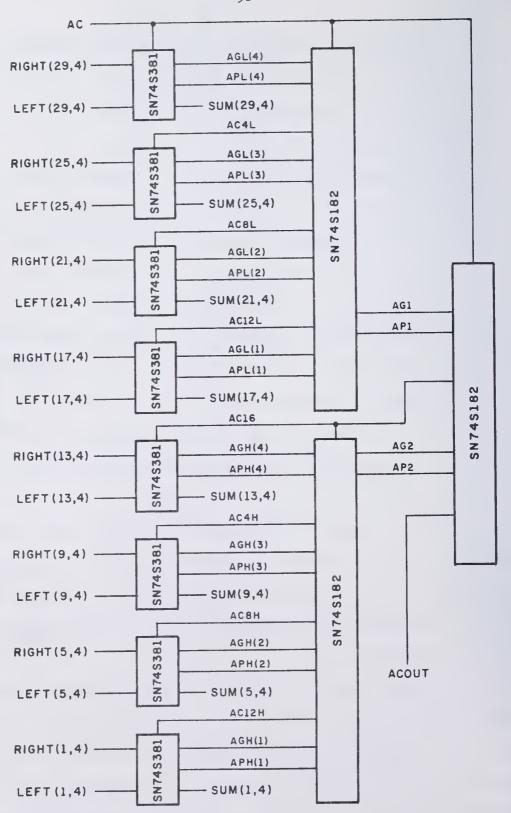

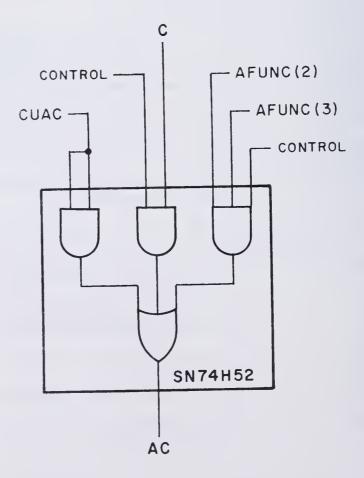

4.2.5.1.6 The Adder

The adder, shown in Figure 4.2.5.1.6-1, accepts two thirty-two bit fractions, LEFT(1,32) and RIGHT(1,32), a function specification, AFUNC(1,24), and an input carry AC. It produces a thirty-two bit output, SUM(1,32), which depends on the input operands, the carry, and the function specification. The SN74S381 arithmetic-logic unit and the SN74S182 look-ahead carry generator.

Figure 4.2.5.1.6-1 The Adder

Figure 4.2.5.1.6-2 The Logic for the Signal AFUNC(1,24)

Except in the case of the integerize function, which is described in section 4.2.5.2.6, each SN74S381 performs the same function, so that AFUNC(1,3)=AFUNC(4,3)=. .=AFUNC(22,3). The functions which can be specified are listed in Table 4.2.5.1.3-1.

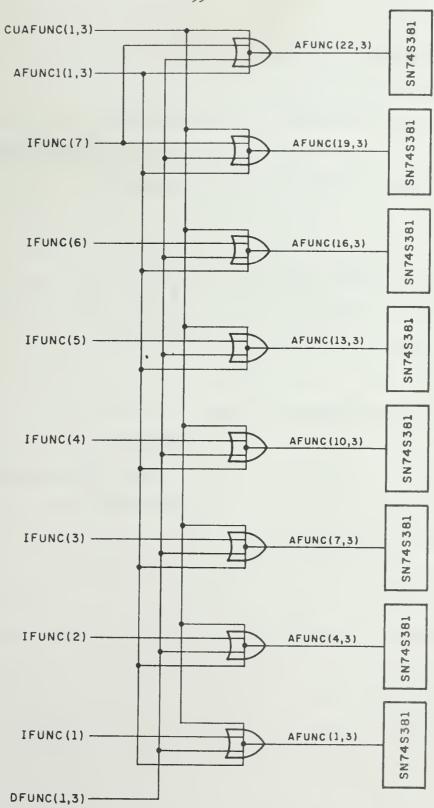

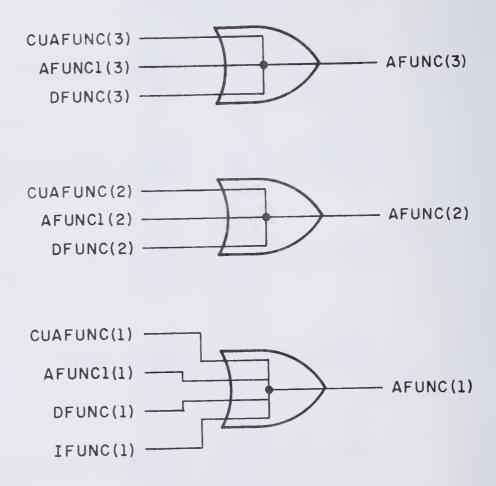

The output of the adder is the thirty-two bit result, SUM(1,32), and the carry out, ACOUT. The function input to the SN74S381's is the result of a wire-OR of four separate tri-state sources. Figures 4.2.5.1.6-2 and 4.2.5.1.6-3 show successively more detail about these wire-ORed signals. Figure 4.2.5.1.6-2 shows eight wire-OR's, each of which produces a three bit function specification. Each of these three bit wire-OR's actually consists of three separate wire-OR's like the three shown in Figure 4.2.5.1.6-3. The details of the signals AFUNC1(1,3), IFUNC(1,8), and CUAFUNC(1,3) will be given in sections 4.2.5.2.1 through 4.2.5.2.6.

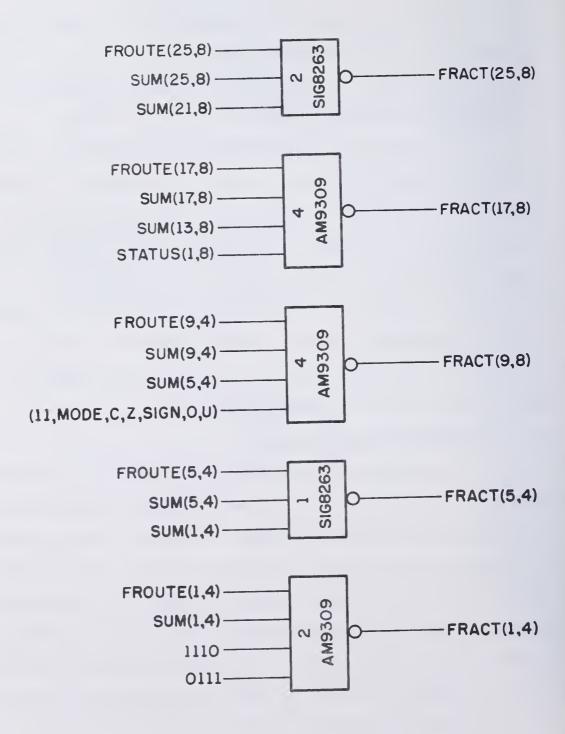

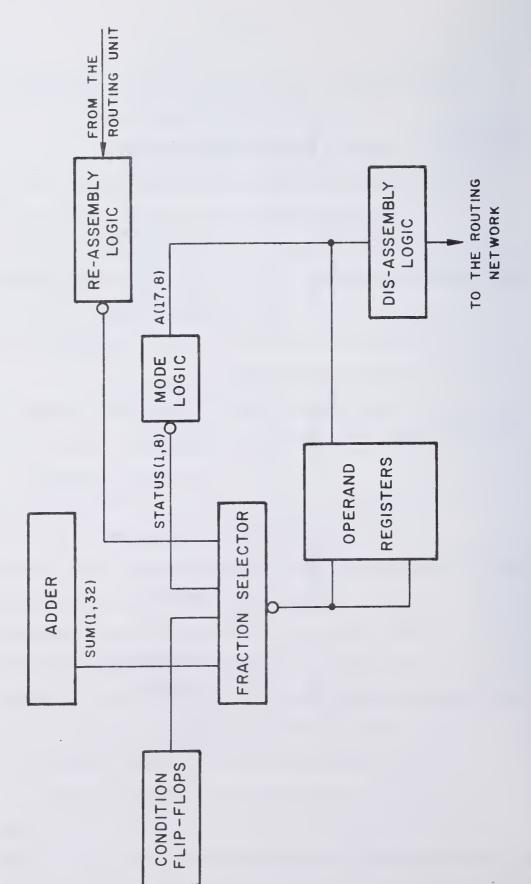

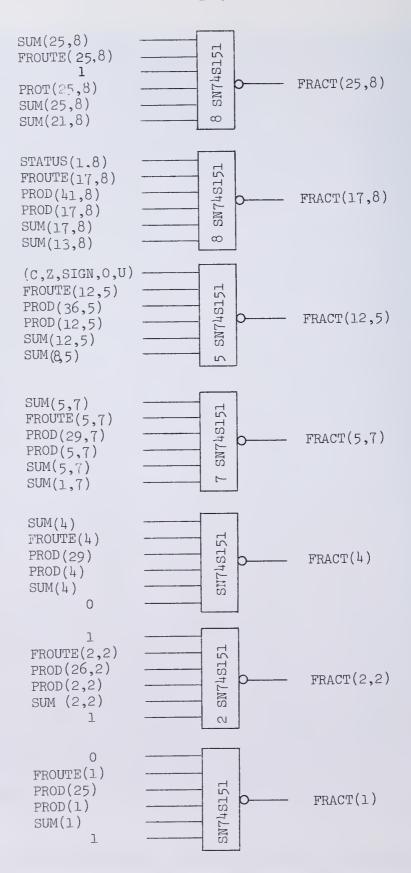

### 4.2.5.1.7 Fraction Selection Logic

The adder operates on active low data primarily because the Signetics 8243 eight position scaler, which is used to perform alignment and normalization shifting, has complemented outputs. Therefore, besides selecting one of five possible fraction sources, the fraction selection logic also performs a logical complement. The logic is shown in Figure 4.2.5.1.7-1, and consists of Signetics 8263 quadruple three-to-one selectors and Advanced Micro Devices AM9309 dual four-to-one selectors. The SIG8263's were used where possible to reduce the package count, and the AM9309's were used because no other four-to-one selector which provides complemented outputs is available.

Figure 4.2.5.1.7-1 The Fraction Selection Logic

The five signals which the fraction selection logic accepts as input are:

- 1. the unmodified output of the Adder, (SUM(1,32).

- 2. The output of the adder shifted right one digit position (four bit positions) by appropriate selection. The control for deciding between this input and input (1) above depends on whether fraction overflow occurs during fraction addition. The details of this control are given in section 4.2.5.2.3. If the shifted input is selected, the high order digit is forced to 1110, complemented to 0001.

- 3. The fraction output from the routing logic reassembly register, FROUTE(1,32). The routing logic is the subject of section 4.3.

- 4. The outputs of the mode flip-flop of section 4.2.5.1.9 and five condition flip-flops (MODE C, Z, SIGN, O, U) which are described in section 4.2.5.1.12, and the output of the status register of the mode logic, STATUS(1,8), which is described in section 4.2.5.1.9. These thirteen bits are supplemented by nineteen bits of ones (complemented to zeros) forced from the SN74S381 arithmetic-logic units (see Table 4.2.5.1.3-1).

- 5. The special fraction overflow shift of one bit position which uses the high order digit value of Olll, complemented to 1000.

This case is fully discussed in section 4.2.5.2.5.

As shown in Figure 4.2.5.1.7-2, the fraction selection logic is in every path which leads to the operand registers. Therefore, one would like it

Figure 4.2.5.1.7-2 The Relationship of the Fraction Selector to the Rest of the Processor

Figure 4.2.5.1.7-3 A Faster Alternative to the Fraction Selection Logic

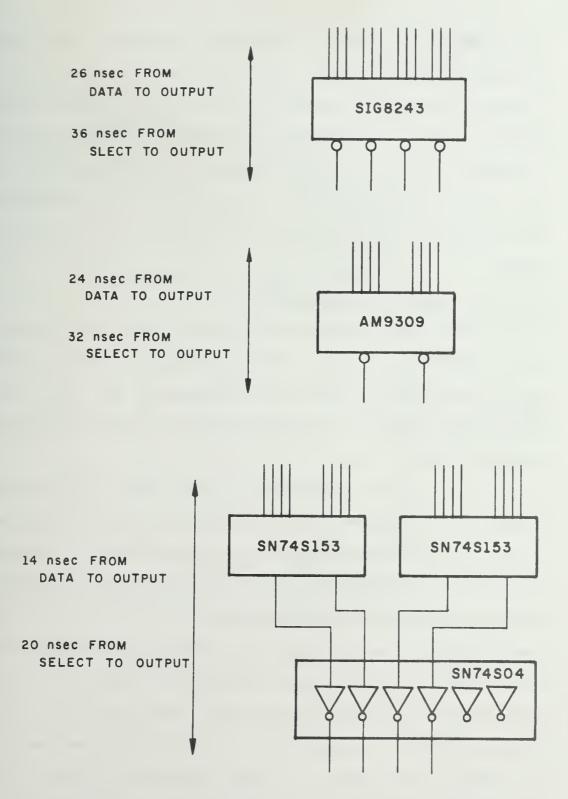

it to be as fast as possible. Unfortunately, neither the SIG8263 nor the AM9309 is available in Schottky form. Figure 4.2.5.1.7-3 shows how the thirteen package logic of Figure 4.2.5.1.7-1 could be replaced by twenty-two packages: sixteen SN74S153 dual non-complementing four-to-one selectors and six SN74S04 inverters. The gain in time is twelve nano-seconds per operation when the timing depends on the data arrival time at the selectors, and sixteen nano-seconds when the timing depends on the arrival time of the selection signals.

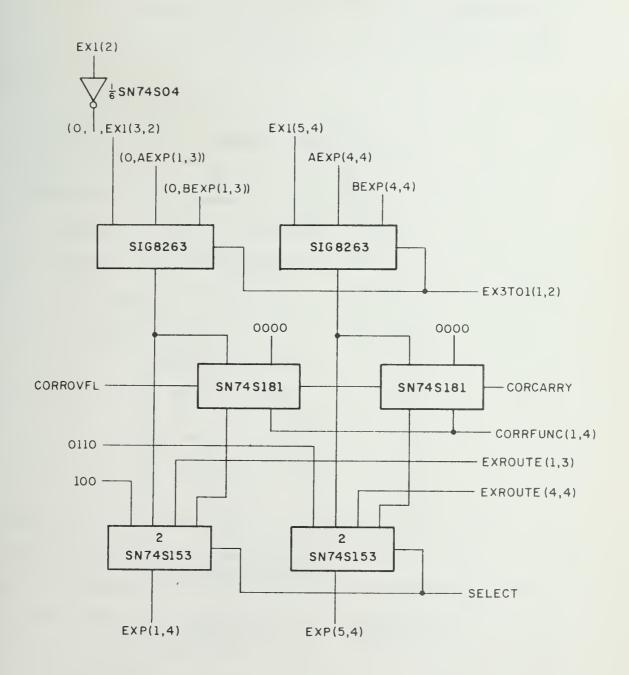

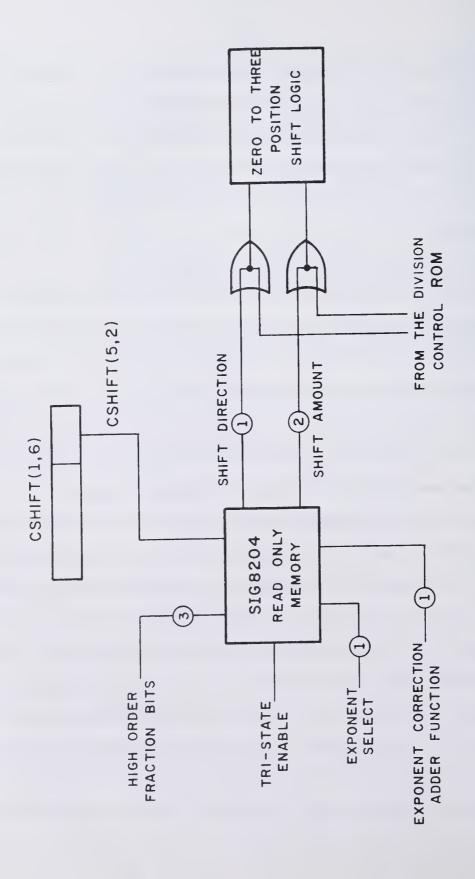

## 4.2.5.1.8 Exponent Correction Adder

The exponent produced by the exponent adder is not correct in all cases. When fraction overflow occurs, the fraction is shifted right one digit position and the exponent must be increased by one. This case and several others discussed in section 4.2.5.2.5 are handled by the exponent correction adder.

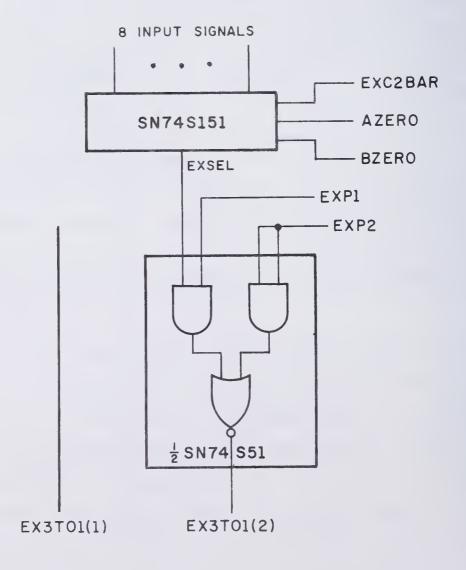

The logic for the exponent correction adder is shown in Figure 4.2.5.1.8-1. It includes two SIG8263 three-to-one selectors which are used to select either the exponent of the left operand, AEXP(1,7), the exponent of the right operand, BEXP(1,7), or the result exponent from the exponent adder, EX1(2,7). Bit EXC1(2) is complemented because it is the bias bit in the biased exponent. When an exponent sum or difference is computed by the exponent adder, the bias bit must be complemented in order for the resulting exponent value to be correctly represented. (See section 4.2.5.1.12.4 or section 4.2.5.1.12.5 for more details.) The logic which produces the selection signal for this selection is shown in Figure 4.2.5.1.8-2. The SN74S151 eight-to-one selector is controlled according to the truth table in

Figure 4.2.5.1.8-1 The Exponent Correction Adder

Figure 4.2.5.1.8-2 The Control Signal for Input Selection for the Exponent Correction Adder

Table 4.2.5.1.8-2; its inputs are wired to the logic constants indicated by Table 4.2.5.1.8-1. EXP1, EXP2, and EX3T01(1) are control signals from the control unit.

| EXC2BAR | AZERO | BZERO | EXSEL<br>OUPTUT |

|---------|-------|-------|-----------------|

| 0       | 0     | 0     | 1               |

| 0       | 0     | 1     | 0               |

| 0       | 1     | 0     | 1               |

| 0       | 1     | 1     | 1               |

| 1       | 0     | 0     | 0               |

| 1       | 0     | 1     | 0               |

| 1       | 1     | 0     | 1               |

| 1       | 1     | 1     | 0               |

Table 4.2.5.1.8-1 The Low-order Bit of Exponent Selection Control

An EXC2BAR value of one means that the left operand has been shifted, so that the correct exponent for a sum or difference is the exponent of the right operand. An AZERO value of zero means that the left operand fraction was zero; a BZERO value of zero means that the right operand fraction was zero. Control signals from the control unit determine the control signal for the exponent selection process according to the truth table in Table 4.2.5.1.8-2.

| Input Signals<br>EXSEL | Output Selection Signal EX3TO1(1,2) | Exponent<br>Selected         |

|------------------------|-------------------------------------|------------------------------|

| х                      | 01                                  | exponent<br>adder<br>value   |

| 1                      | 10                                  | left<br>operand<br>exponent  |

| 0                      | 11                                  | right<br>operand<br>exponent |

Table 4.2.5.1.8-2 Exponent Selection Control

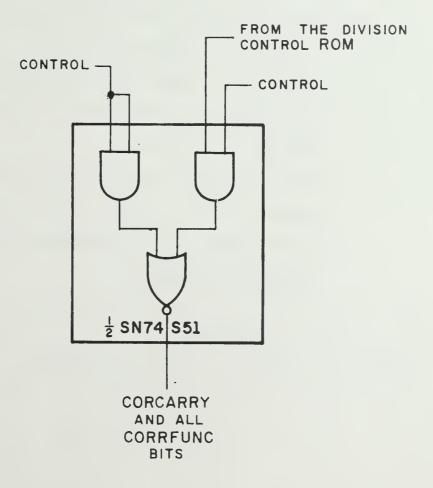

The SN74S181 arithmetic-logic units are used to either add or subtract one from the selected exponent. The values of CORCARRY and CORRFUNC(1,4) necessary to accomplish this are given in Table 4.2.5.1.8-3 which is based on the operating details of the SN74S181 (Texas Instruments Corporation, 1973, p. 383).

| Inputs        |          | SN74S181 Output   |

|---------------|----------|-------------------|

| CORRFUNC(1,4) | CORCARRY | DN   4DIOI OUOPUO |

| 0000          | 0        | exponent + 1      |

| 1111          | 1        | exponent - 1      |

Table 4.2.5.1.8-3 Control of Exponent Correction Add

The control logic shown in Figure 4.2.5.1.8-3 supplies the CORCARRY and CORRFUNC(1,4) signals. The signal from the division control ROM is explained in section 4.2.5.2.5. The final stage of the exponent correction adder

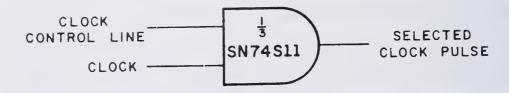

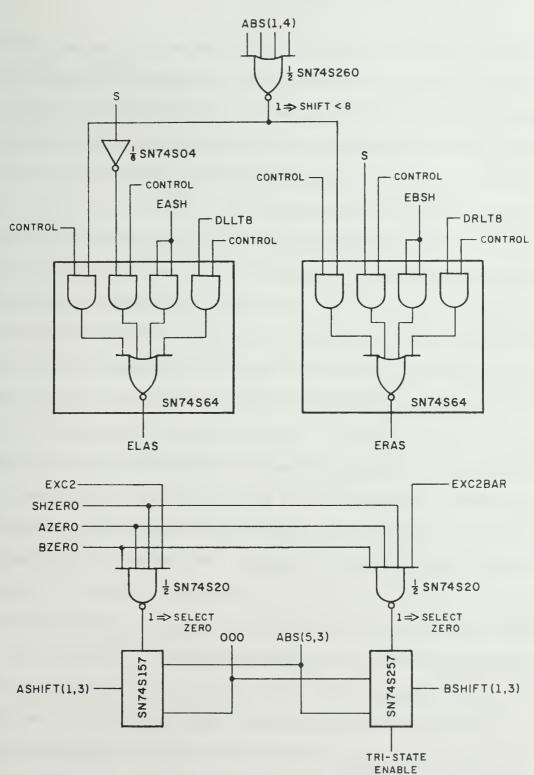

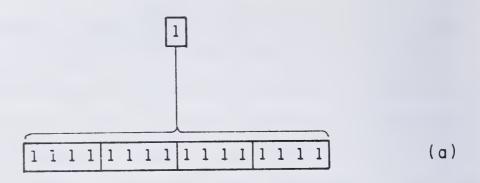

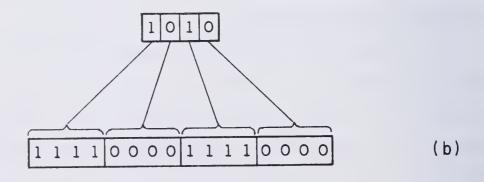

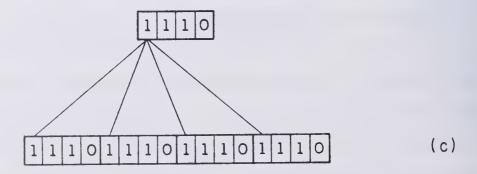

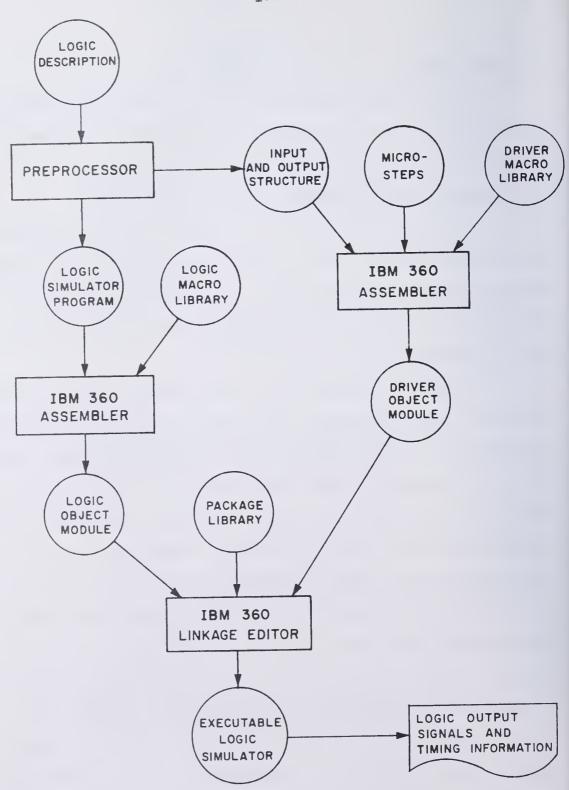

Figure 4.2.5.1.8-3 The CORCARRY and CORRFUNC(1,4) Bits for Exponent Correction Adder Control